瑞薩 RL78/F13 LIN 通信收發問題排查與解決經驗

一、問題背景

在專案開發過程中,常常會出現第一版 IDE 配置完成後,後續研發人員直接沿用的情況。然而,部分 IDE 配置可能與硬體設定存在深度綁定,如果實際上 MCU 的硬體存在變更,可能會導致管腳功能不匹配,從而出現調試異常的情況。本文以一個因 LIN 介面存在變動而導致 LIN 通信無法進行正常收發的案例為例,分享具體的問題排查與解決經過。

二、軟硬體背景

本次實例所用 IDE 為瑞薩 CS+,晶片型號為 RL78/F13 (64-pin 16 bit MCU)。故障現象為 LIN 節點無報文,示波器測量單片機引腳均為高電平,初步排查已排除硬體問題可能。接下來詳細分析具體的問題排查與解決步驟。

三、問題描述與排查步驟

檢查原理圖和晶片引腳圖

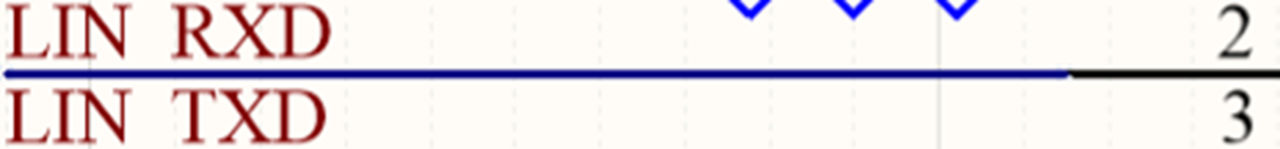

首先檢查原理圖, 確認 LIN 的 RXD 和 TXD 兩個收信和送信引腳連的是晶片 2 和 3 pin,如下圖 (圖1) 所示:

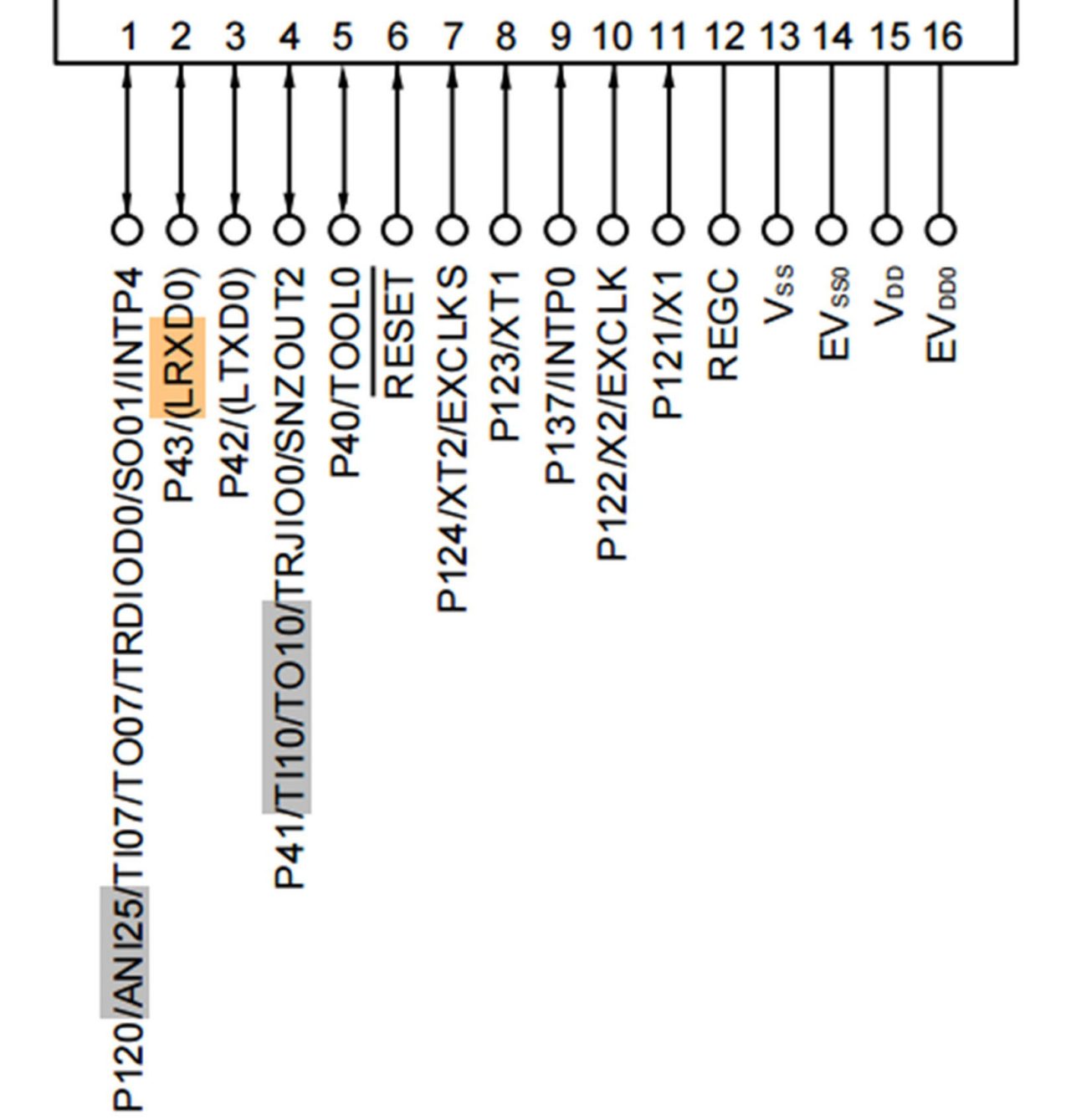

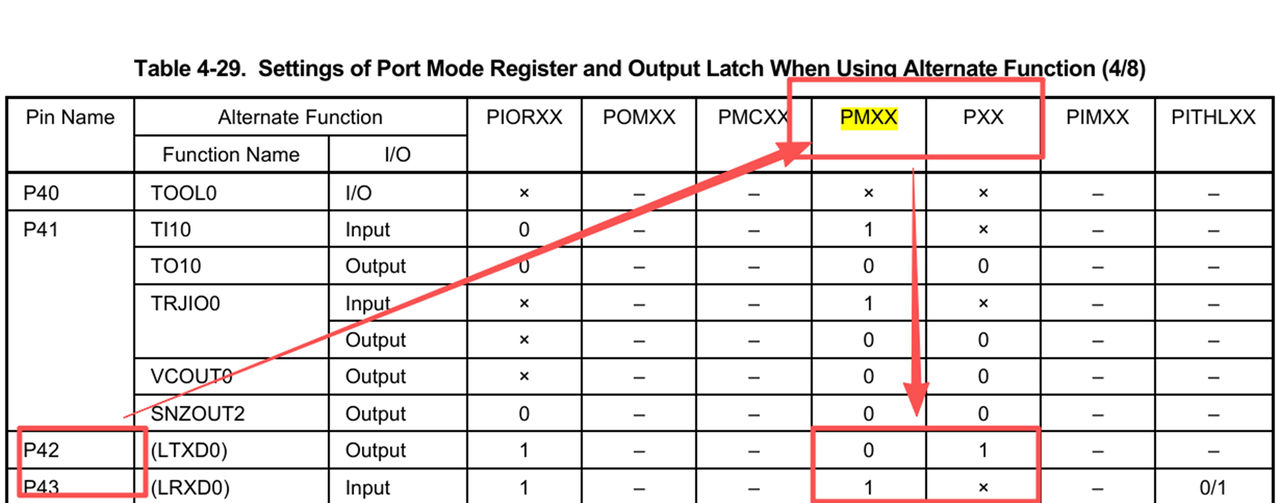

根據下圖 (圖2) 瑞薩 RL78/F13 的硬體使用者手冊,這兩個引腳對應的是 Port 編號是 P42 和 P43。這個資訊對後續配置至關重要。

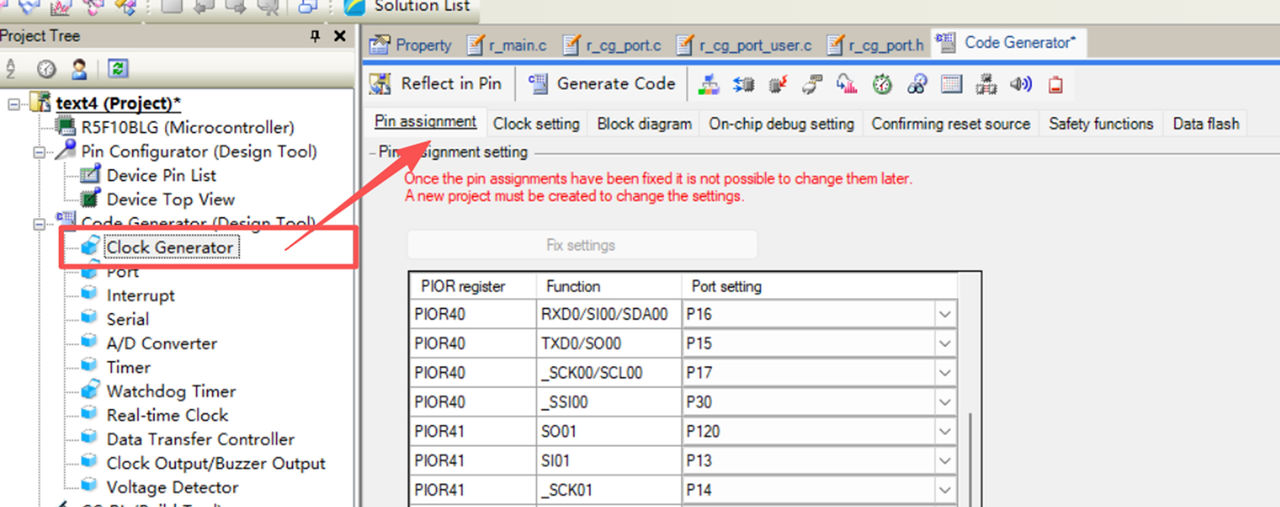

检查 CS+ 管脚分配界面

如下图 (图3) 所示,打开 CS+ 的 Clock Generator → Pin Assignment 以检查寄存器功能映射的配置界面,发现 LTxD0 和 LRxD0 对应的 LIN 收发功能所对应的 PIO 寄存器被映射到了 P13 和 P14,与原理图中的 P42、P43 不一致。

这意味着 LIN 收发功能实际上被分配给了 P13 和 P14,而硬件实际使用的 P42 和 P43 并未被赋予相应的外设功能,因此无法执行 LIN 通信所需的收发操作。

新建工程,選擇配置到正確的 Port 上

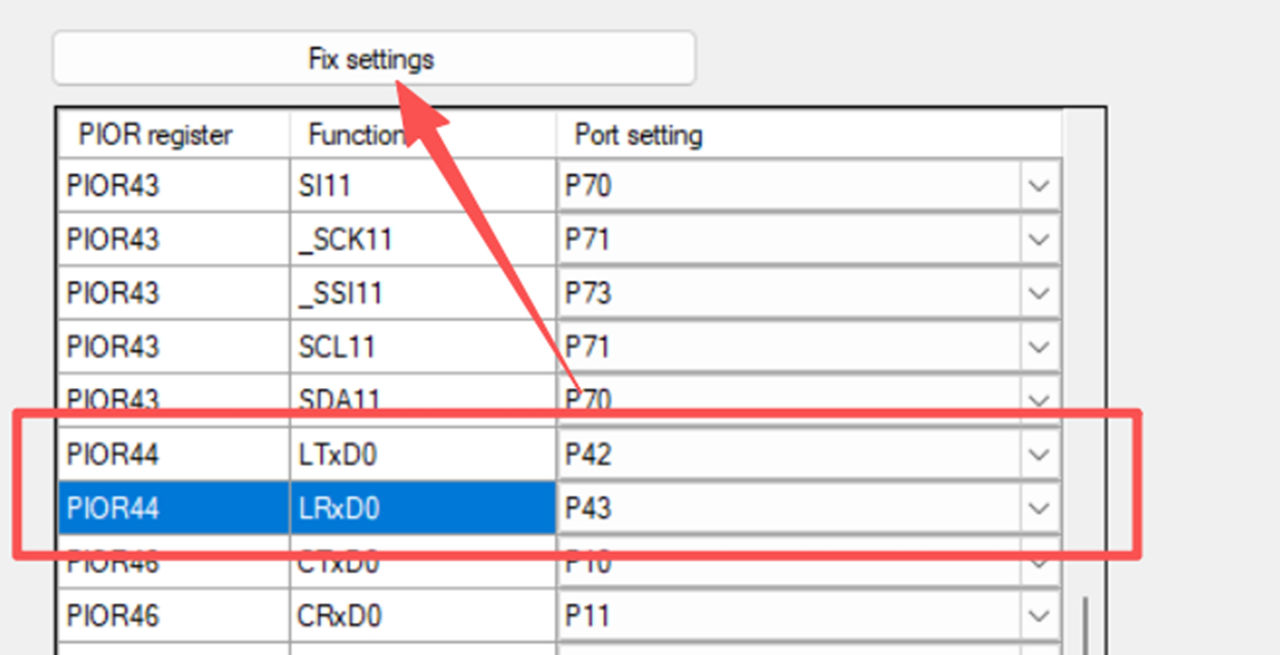

新建工程後,在 Pin Assignment 中將 LIN 收發功能正確分配至 P42 與 P43,並點擊 Fix Setting。需要注意,由於 CS+ 一旦執行 Fix setting 就不能再修改該配置,所以修改前需考慮清楚。

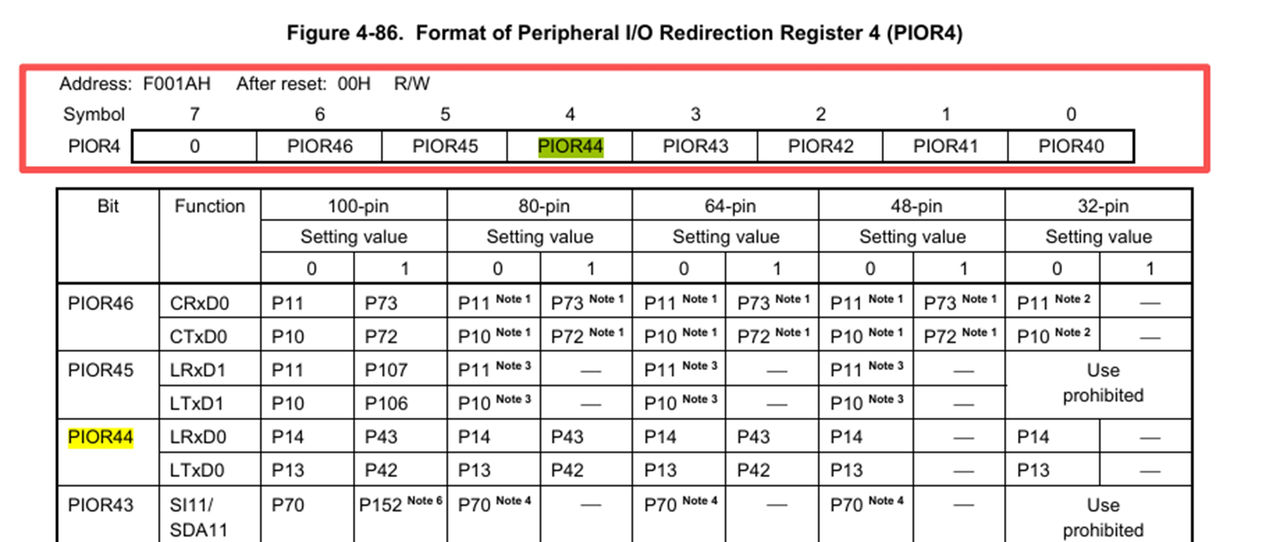

晶片手冊解讀 PIOR4

PIOR 是 Peripheral I/O Redirection Register 的縮寫,對應本案例的 PIOR 是其第四組。如下圖 (圖6) 紅色標記代表該寄存器中的每一位分別控制不同埠的功能映射。該寄存器的每一位的代表的每一個埠號,例如 PIOR44 位於其第 4 比特位,通過設置該位可實現 LRxD0 與 LTxD0 功能的開啟或關閉。

PIOR44 寄存器設定介紹

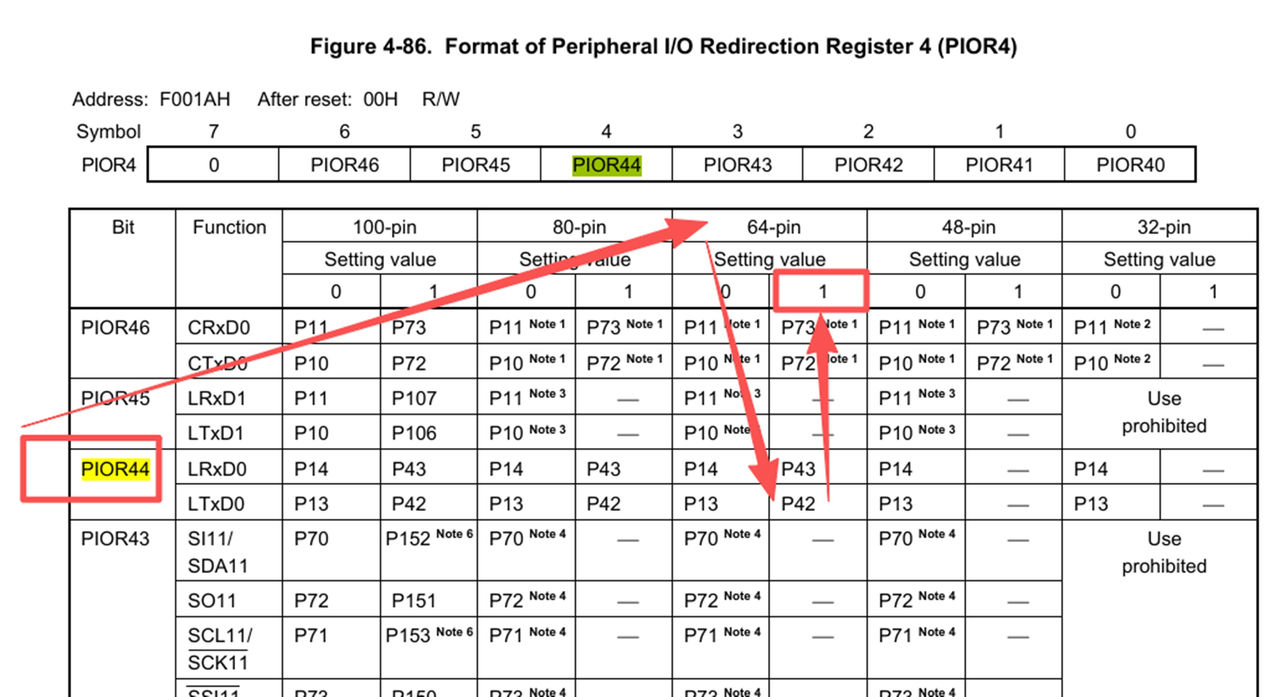

查閱晶片手冊中有關 PIOR44 的詳細說明,按照下圖 (圖7) 紅色箭頭標記順序,可根據引腳封裝類型找到對應配置項。首先確認晶片為 64-pin 封裝,再找到 64-pin 裡 P42 和 P43 這兩個埠的啟用設置值。根據手冊說明,該值設為 1 時,對應的設置是 P42 與 P43;設為 0 時,則對應 P13 與 P14。由於實際原理圖使用的是 P42 與 P43,因此需要將此值設置為 1。

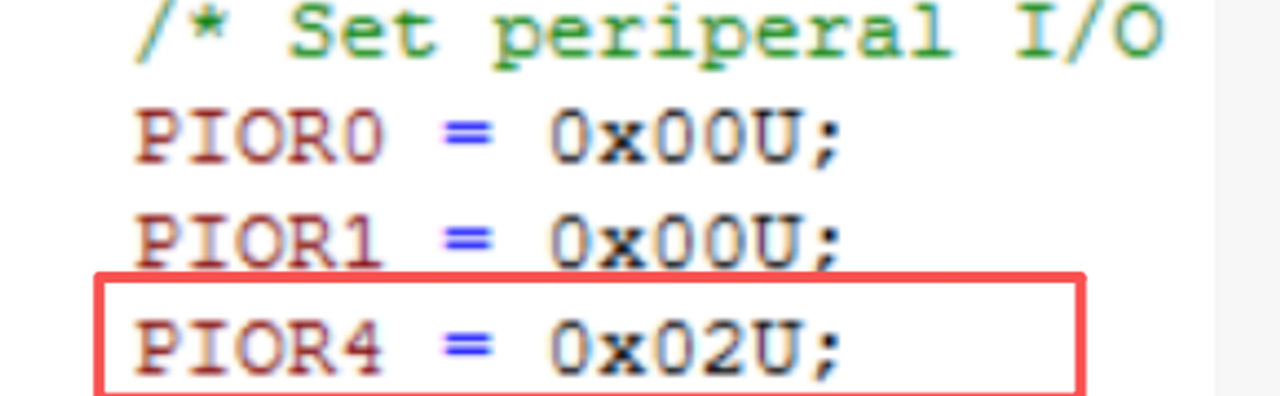

查詢代碼 PIOR4 和手冊對照

搜索代碼找到該寄存器的設定代碼行,發現當前設定值為 0X02U,如下圖 (圖8) 所示:

U 表示有八位元 16 進制數目,換成二進位展開為 0000 0010,其中第五位是 0。根據前面手冊提示,對於 64-pin 的版本,該位為 0 時對應 P13 和 P14,為 1 時對應 P42 和 P43。

由於當前值為 0,即 LIN 功能仍被分配至 P13 和 P14,與硬體設計不符。因此需將此位修改為 1,即將二進位改為 0001 0010,換成 16 進制是 0x12。所以將代碼中的 PIOR4 = 0x02U; 修改為 PIOR4 = 0x12U; 。

開啟後表示可以使用 PIOR44 的 P42 和 P43 作為LIN 收發功能了,然後再去具體設定 P42 和 P43 相關的寄存器,設置輸入輸出設定。

查詢 P42 和 P43 配置描述

根據手冊表格顯示,使用 P42 和 P43 進行 LIN 收發需要配置相關的 PMxx 和 Pxx (xx 是略寫,實際上是對應的相關數位) 對應的模式寄存器,P42 作為輸出對應的 PMxx 要改成 0,對應 Pxx 要改成 1。P43 作為輸入 PMxx 要改成 1,對應的 Pxx 不用設置。如表中還會看見需要配置 PIOR,但是我們之前已經配置過了,所以不用管。

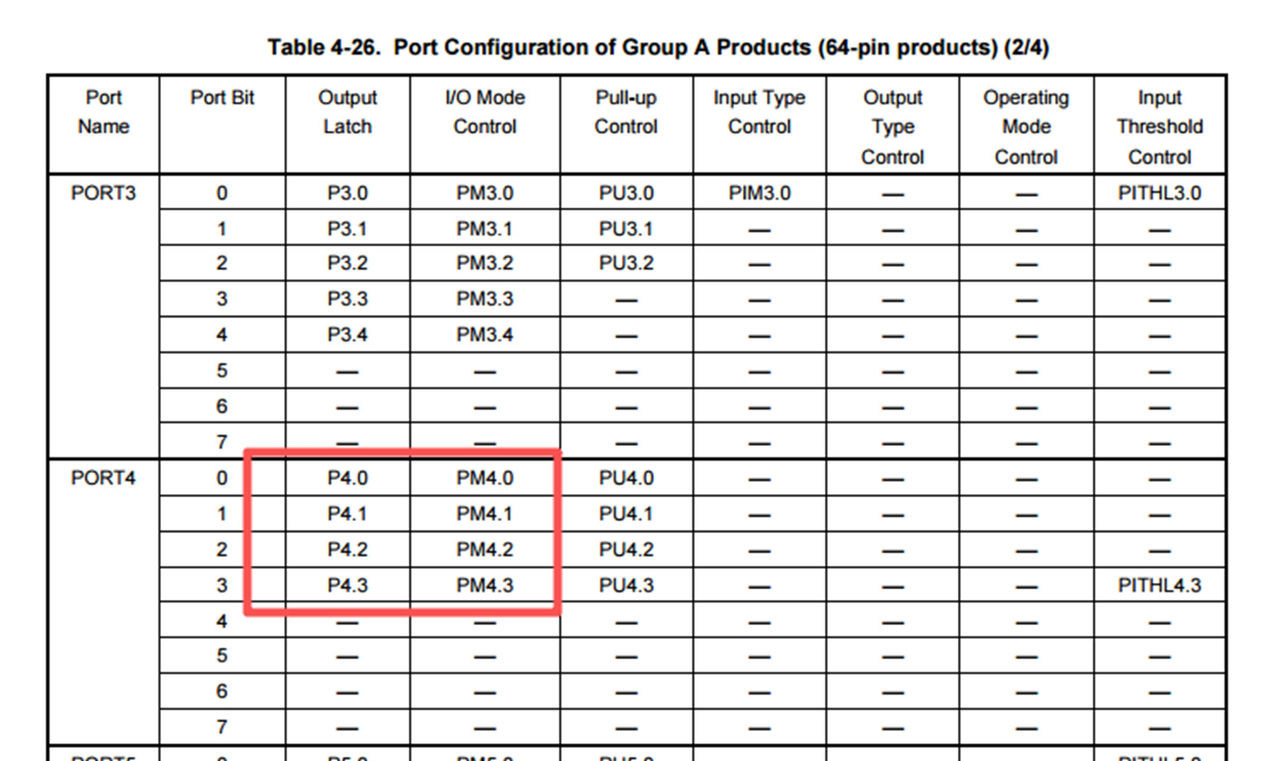

查詢 LIN 收發相關寄存器設定

跟著手冊目錄找到對應 PORT 的章節 (在第 309 頁),P42 對應的 IO 模式寄存器和 Output Latch 的名稱是 P4.2 和 PM4.2,P43 是 PM4.3 和 P4.3,接下來再去完成代碼的設置。

檢查代碼,編譯進行調試

在代碼中檢查 P42 與 P43 的相關配置,搜索代碼發現如下圖 (圖11) 配置,P42 目前被設置為 LTxD (輸出),其配置如下:

- P4.2 = 1;

- PM4.2 = 0;

以上設置符合輸出模式要求,無需修改。

隨後按照此步驟繼續檢查 PM4.3 和 P4.3 的配置,確認其 LTXD 收信端配置是否正確,若未設置或設置不正確,需修改成對應的值。最後保存並編譯代碼,連接 LIN 調試工具進行驗證。此時可觀察到 LIN 調試工具可正常出現 LIN 的收發報文,表明修改成功。最後保存並編譯代碼,連接 LIN 調試工具進行驗證。此時可觀察到 LIN 調試工具可正常出現 LIN 的收發報文,表明修改成功。

四、總結

本文通過瑞薩RL78/F13 LIN通信無法正常收發的實際案例,詳細介紹了因硬體引腳變更導致功能配置不匹配的問題分析與解決過程,重點說明了如何通過核對原理圖、調整IDE引腳分配、解讀並配置PIOR寄存器及相關埠寄存器,最終實現LIN收發功能恢復的完整步驟。

欲瞭解關於更多瑞薩相關方案或技術資訊,請與駿龍科技當地的辦事處聯繫或點擊下方「聯繫我們」,提交您的需求,駿龍科技公司願意為您提供更詳細的技術解答。

更多資訊: