瑞萨 RL78/F13 LIN 通信收发问题排查与解决经验

一、问题背景

在项目开发过程中,常常会出现第一版 IDE 配置完成后,后续研发人员直接沿用的情况。然而,部分 IDE 配置可能与硬件配置存在深度绑定,如果实际上 MCU 的硬件存在变更,可能会导致管脚功能不匹配,从而出现调试异常的情况。本文以一个因 LIN 接口存在变动而导致 LIN 通信无法进行正常收发的案例为例,分享具体的问题排查与解决经过。

二、软硬件背景

本次实例所用 IDE 为瑞萨 CS+,芯片型号为 RL78/F13 (64-pin 16 bit MCU)。故障现象为 LIN 节点无报文,示波器测量单片机引脚均为高电平,初步排查已排除硬件问题可能。接下来详细分析具体的问题排查与解决步骤。

三、问题描述与排查步骤

检查原理图和芯片引脚图

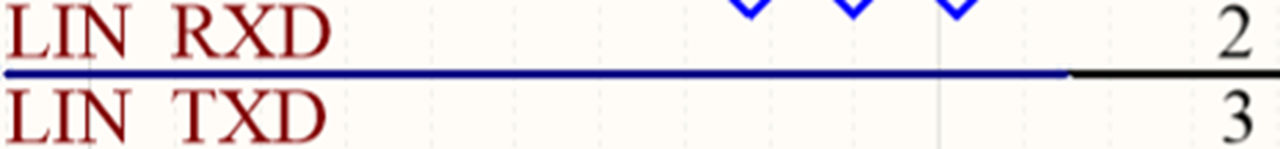

首先检查原理图, 确认 LIN 的 RXD 和 TXD 两个收信和送信引脚连的是芯片 2 和 3 pin,如下图 (图1) 所示:

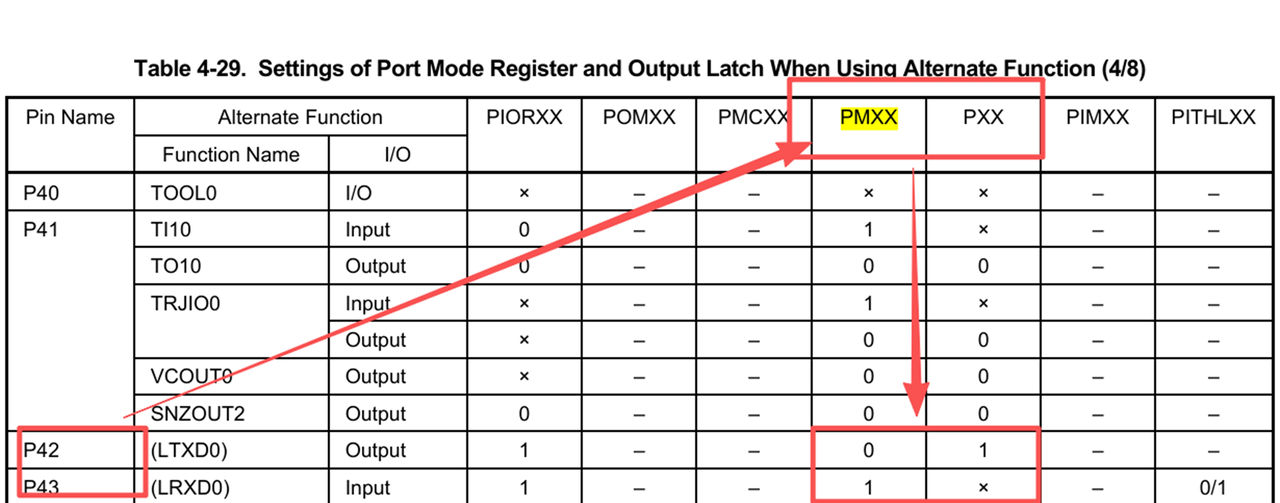

根据下图 (图2) 瑞萨 RL78/F13 的硬件用户手册,这两个引脚对应的是 Port 编号是 P42 和 P43。这个信息对后续配置至关重要。

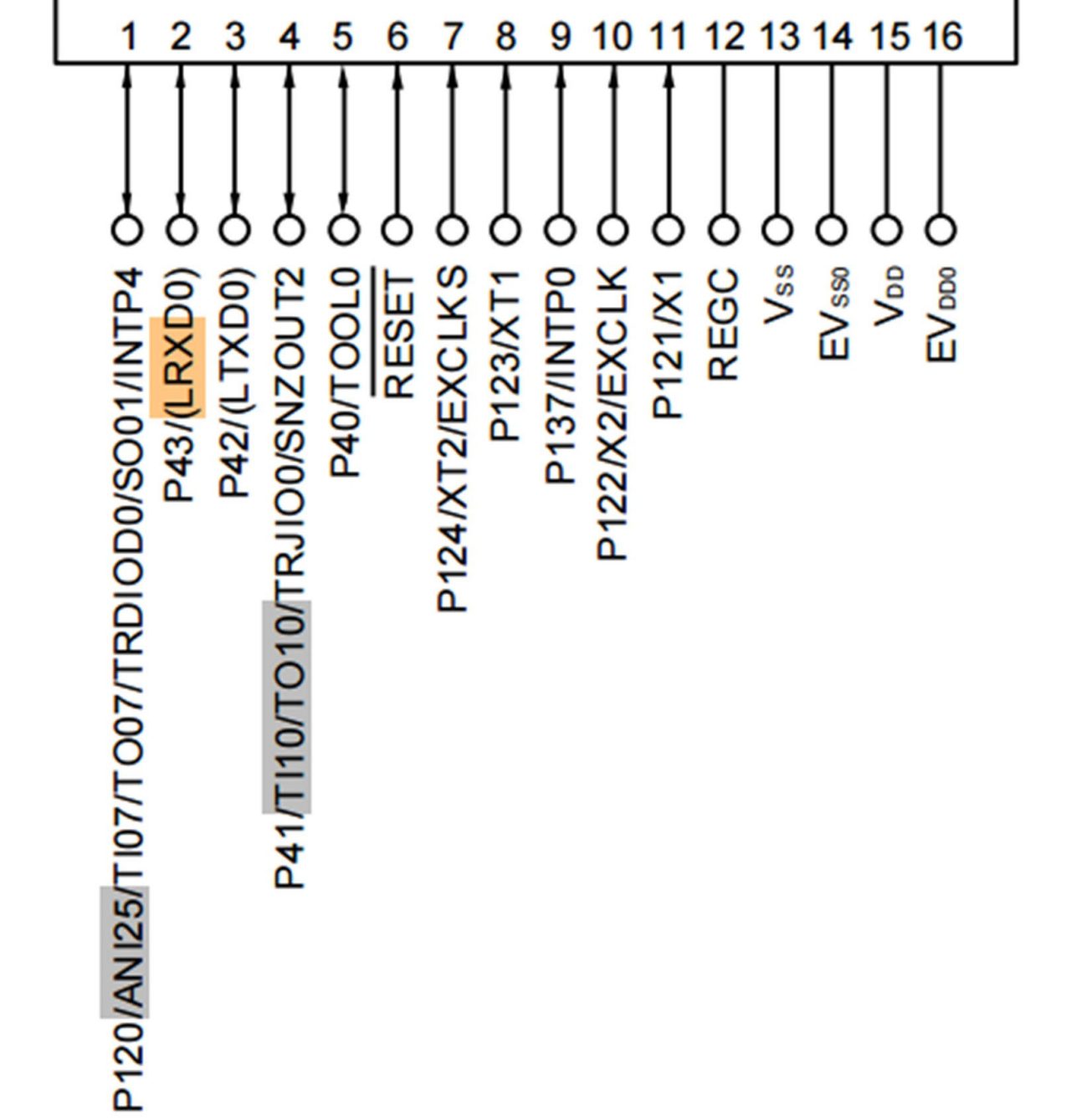

检查 CS+ 管脚分配界面

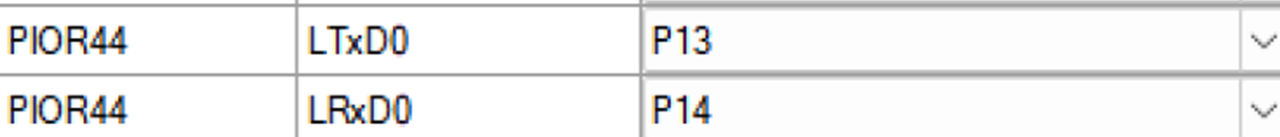

如下图 (图3) 所示,打开 CS+ 的 Clock Generator → Pin Assignment 以检查寄存器功能映射的配置界面,发现 LTxD0 和 LRxD0 对应的 LIN 收发功能所对应的 PIO 寄存器被映射到了 P13 和 P14,与原理图中的 P42、P43 不一致。

这意味着 LIN 收发功能实际上被分配给了 P13 和 P14,而硬件实际使用的 P42 和 P43 并未被赋予相应的外设功能,因此无法执行 LIN 通信所需的收发操作。

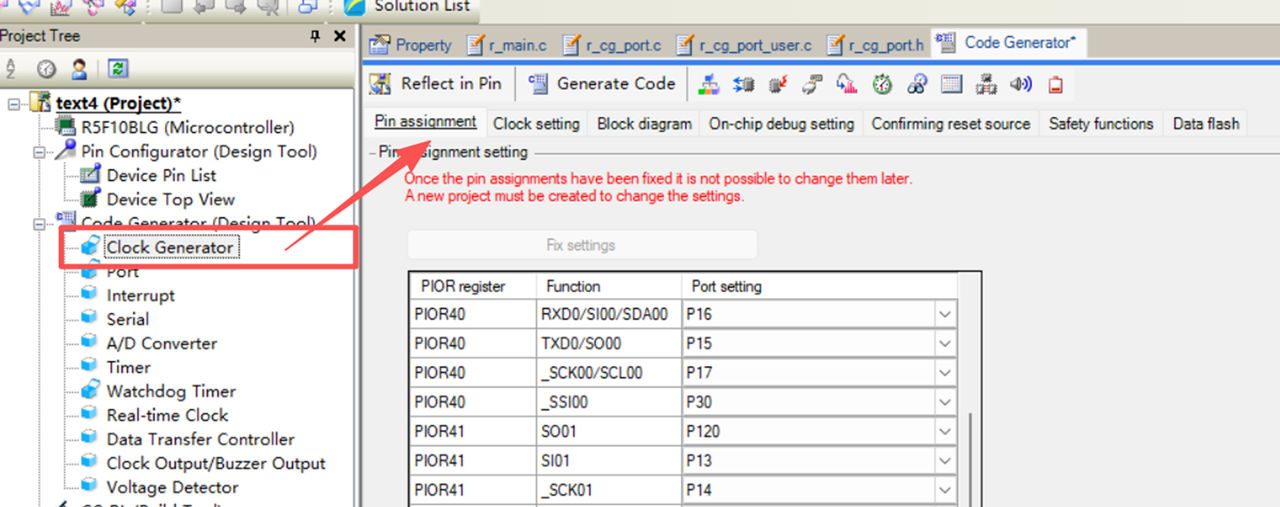

新建工程,选择配置到正确的 Port 上

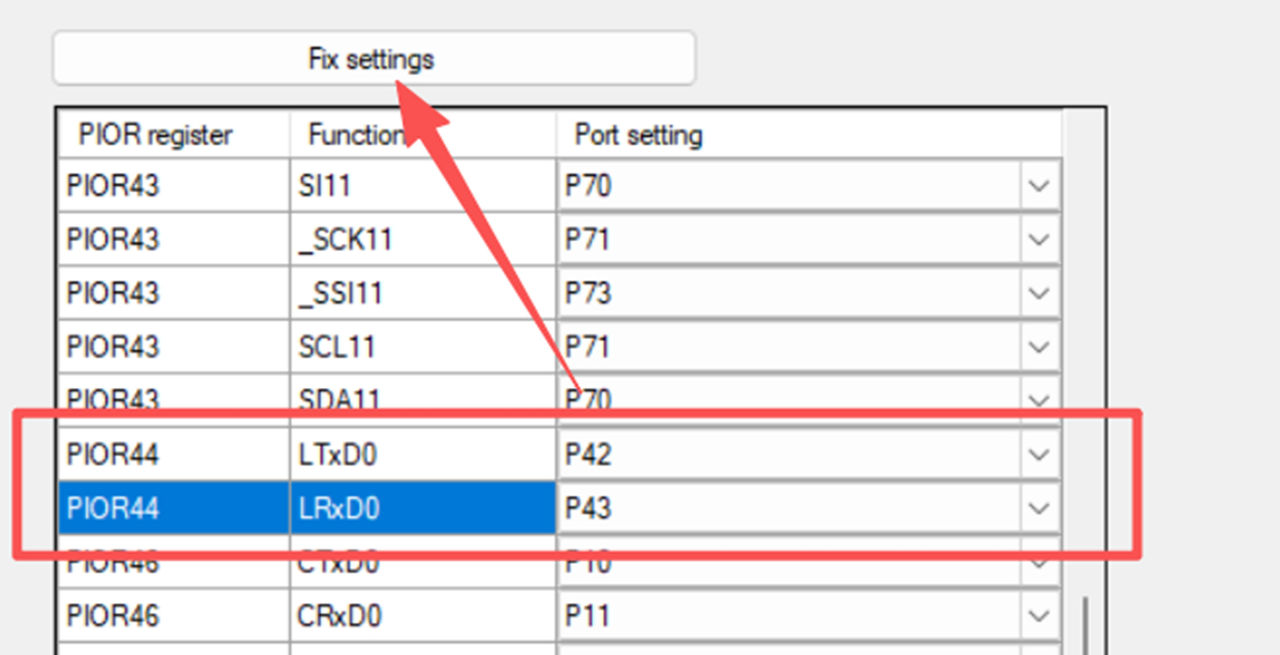

新建工程后,在 Pin Assignment 中将 LIN 收发功能正确分配至 P42 与 P43,并点击 Fix Setting。需要注意,由于 CS+ 一旦执行 Fix setting 就不能再修改该配置,所以修改前需考虑清楚。

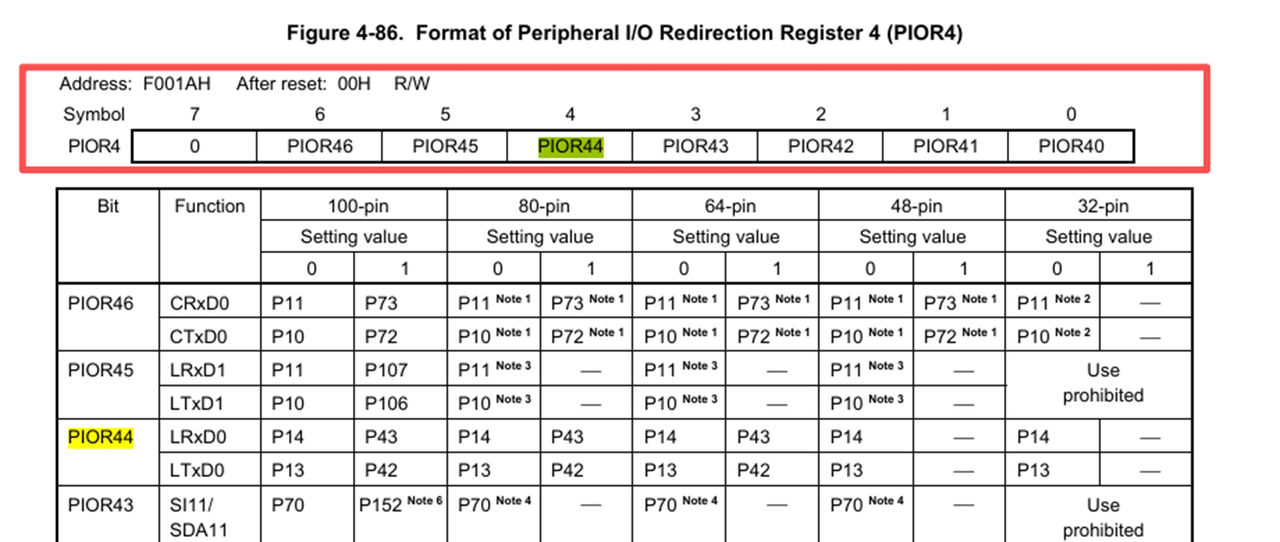

芯片手册解读 PIOR4

PIOR 是 Peripheral I/O Redirection Register 的缩写,对应本案例的 PIOR 是其第四组。如下图 (图6) 红色标记代表该寄存器中的每一位分别控制不同端口的功能映射。该寄存器的每一位的代表的每一个端口号,例如 PIOR44 位于其第 4 比特位,通过设置该位可实现 LRxD0 与 LTxD0 功能的开启或关闭。

PIOR44 寄存器设定介绍

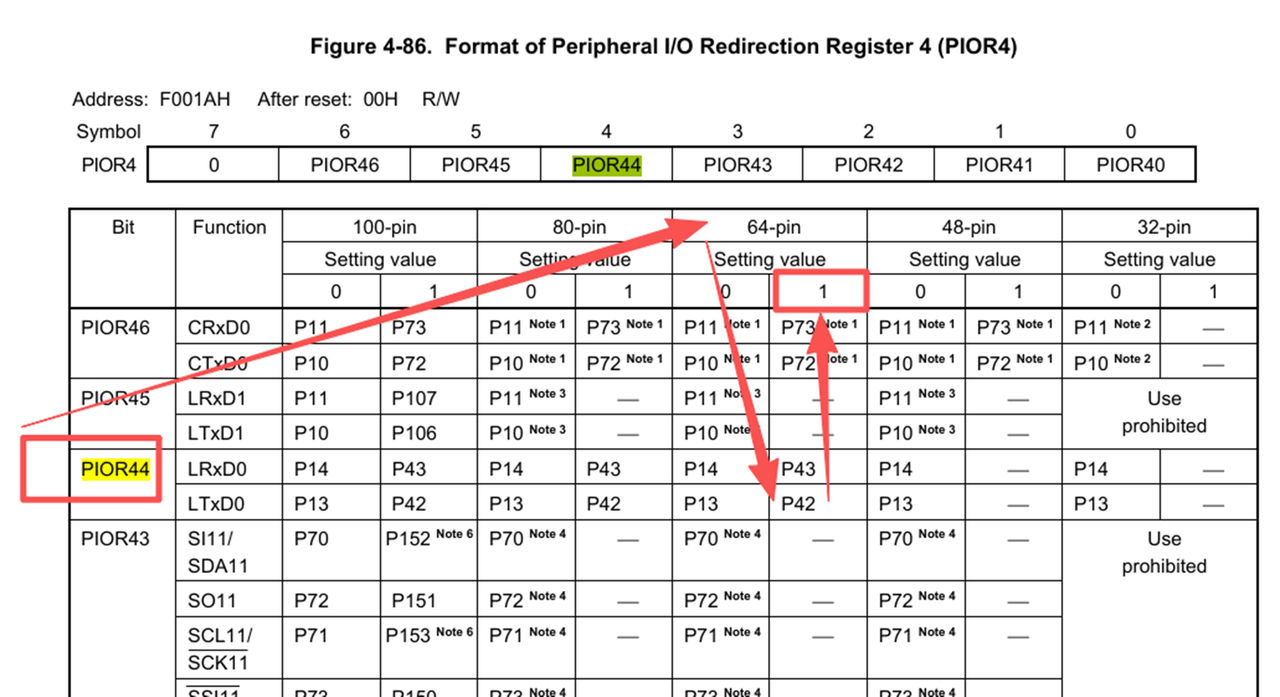

查阅芯片手册中有关 PIOR44 的详细说明,按照下图 (图7) 红色箭头标记顺序,可根据引脚封装类型找到对应配置项。首先确认芯片为 64-pin 封装,再找到 64-pin 里 P42 和 P43 这两个端口的启用设置值。根据手册说明,该值设为 1 时,对应的设置是 P42 与 P43;设为 0 时,则对应 P13 与 P14。由于实际原理图使用的是 P42 与 P43,因此需要将此值设置为 1。

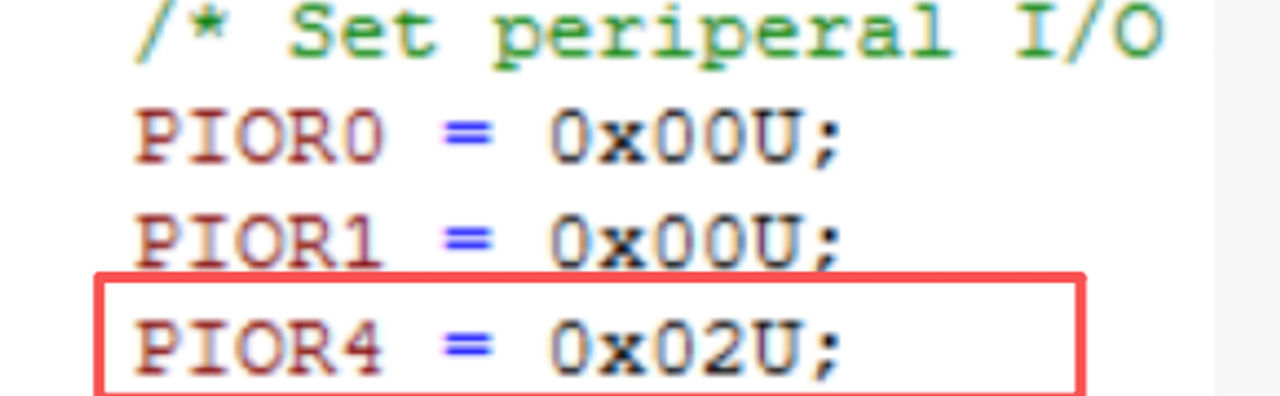

查询代码 PIOR4 和手册对照

搜索代码找到该寄存器的设定代码行,发现当前设定值为 0X02U,如下图 (图8) 所示:

U 表示有八位 16 进制数目,换成二进制展开为 0000 0010,其中第五位是 0。根据前面手册提示,对于 64-pin 的版本,该位为 0 时对应 P13 和 P14,为 1 时对应 P42 和 P43。

由于当前值为 0,即 LIN 功能仍被分配至 P13 和 P14,与硬件设计不符。因此需将此位修改为 1,即将二进制改为 0001 0010,换成 16 进制是 0x12。所以将代码中的 PIOR4 = 0x02U; 修改为 PIOR4 = 0x12U; 。

开启后表示可以使用 PIOR44 的 P42 和 P43 作为LIN 收发功能了,然后再去具体设定 P42 和 P43 相关的寄存器,设置输入输出设定。

查询 P42 和 P43 配置描述

根据手册表格显示,使用 P42 和 P43 进行 LIN 收发需要配置相关的 PMxx 和 Pxx (xx 是略写,实际上是对应的相关数字) 对应的模式寄存器,P42 作为输出对应的 PMxx 要改成 0,对应 Pxx 要改成 1。P43 作为输入 PMxx 要改成 1,对应的 Pxx 不用设置。如表中还会看见需要配置 PIOR,但是我们之前已经配置过了,所以不用管。

查询 LIN 收发相关寄存器设定

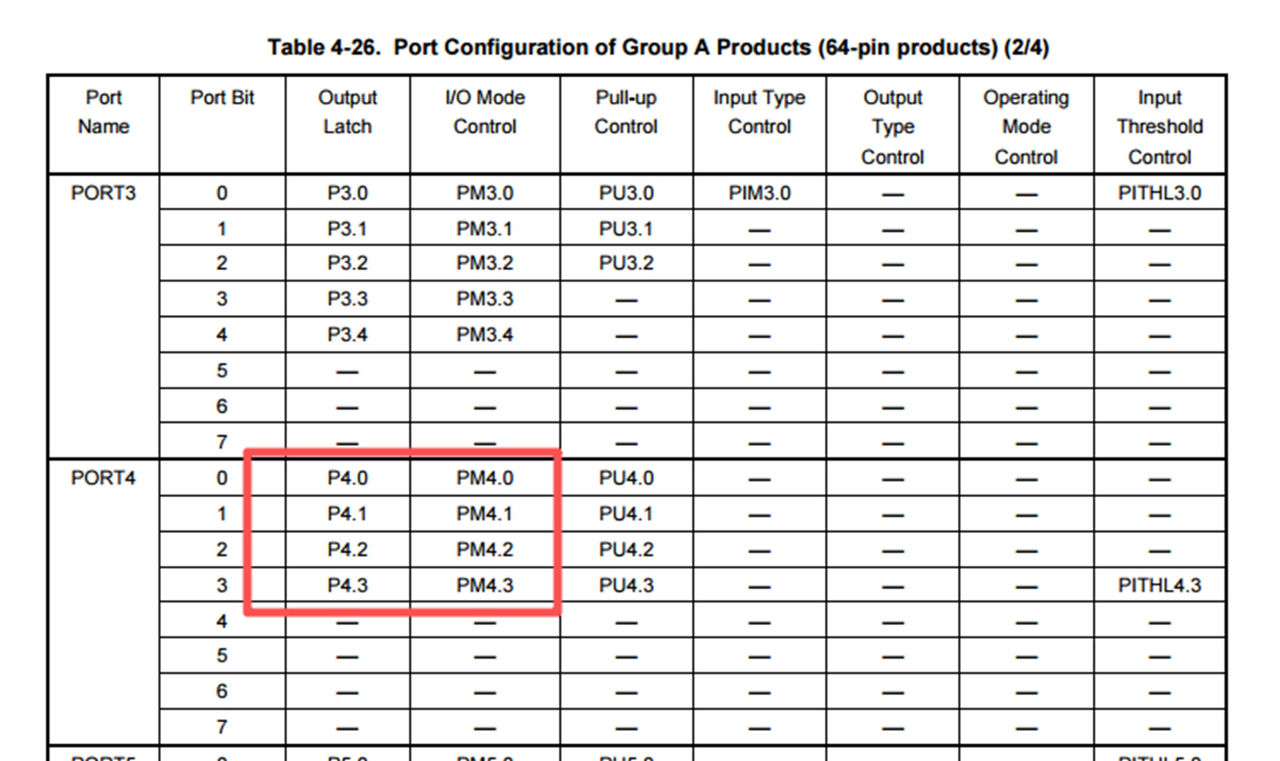

跟着手册目录找到对应 PORT 的章节 (第 309 页),P42 对应的 IO 模式寄存器和 Output Latch 的名称是 P4.2 和 PM4.2,P43 是 PM4.3 和 P4.3,接下来再去完成代码的设置。

检查代码,编译进行调试

在代码中检查 P42 与 P43 的相关配置,搜索代码发现配置如下,P42 目前被设置为 LTxD (输出)。

- P4.2 = 1;

- PM4.2 = 0;

以上设置符合输出模式要求,无需修改。

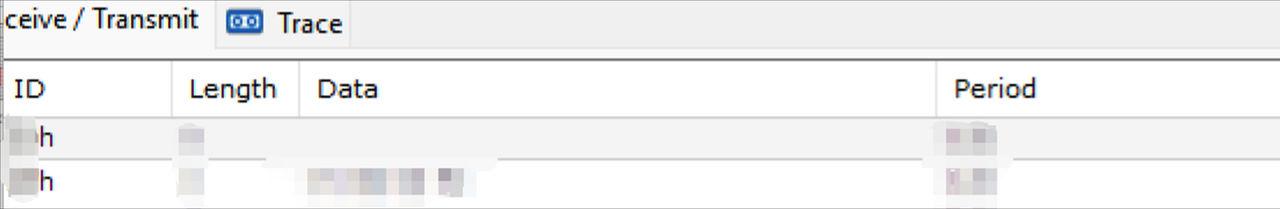

随后按照此步骤继续检查 PM4.3 和 P4.3 的配置,确认其 LTXD 收信端配置是否正确,若未设置或设置不正确,需修改成对应的值。最后保存并编译代码,连接 LIN 调试工具进行验证。此时可观察到 LIN 调试工具可正常出现 LIN 的收发报文,表明修改成功。最后保存并编译代码,连接 LIN 调试工具进行验证。此时可观察到 LIN 调试工具可正常出现 LIN 的收发报文,表明修改成功。

四、总结

本文通过瑞萨 RL78/F13 LIN 通信无法正常收发的实际案例,详细介绍了因硬件引脚变更导致功能配置不匹配的问题分析与解决过程,重点说明了如何通过核对原理图、调整 IDE 引脚分配、解读并配置 PIOR 寄存器及相关端口寄存器,最终实现 LIN 收发功能恢复的完整步骤。

欲了解关于更多瑞萨相关方案或技术信息,请与骏龙科技当地的办事处联系或点击下方「联系我们」,提交您的需求,骏龙科技公司愿意为您提供更详细的技术解答。

更多信息: