英飞凌 MOSFET datasheet 详解——那些你需要关注的关键参数与典型应用 (中)

在《英飞凌 MOSFET datasheet 详解——那些你需要关注的关键参数与典型应用 (上)》一文中,我们详细解读了 MOSFET 数据手册中的四个核心参数:功率损耗、漏极电流、安全工作区(SOA)和瞬态热阻抗。

本文将延续上篇的内容,继续解读 MOSFET 数据手册中的另外五个关键参数:雪崩特性、VGS(th)、寄生电容与栅极电荷、体二极管以及热阻。这些参数直接影响 MOSFET 的开关性能、可靠性和热设计,是深入理解和选型的关键。

一、Avalanche(雪崩)

MOSFET 雪崩是指当 MOSFET 上所承受的电压超过其击穿电压时,在强电场作用下,载流子(电子和空穴)获得足够高的能量,通过碰撞电离产生新的电子 - 空穴对,形成连锁反应,导致电流急剧增大的现象。该现象类似于雪崩,初始的少量载流子在强电场中迅速引发大量载流子的产生和流动,从而可能造成 MOSFET 器件的损坏,影响其正常工作和性能。

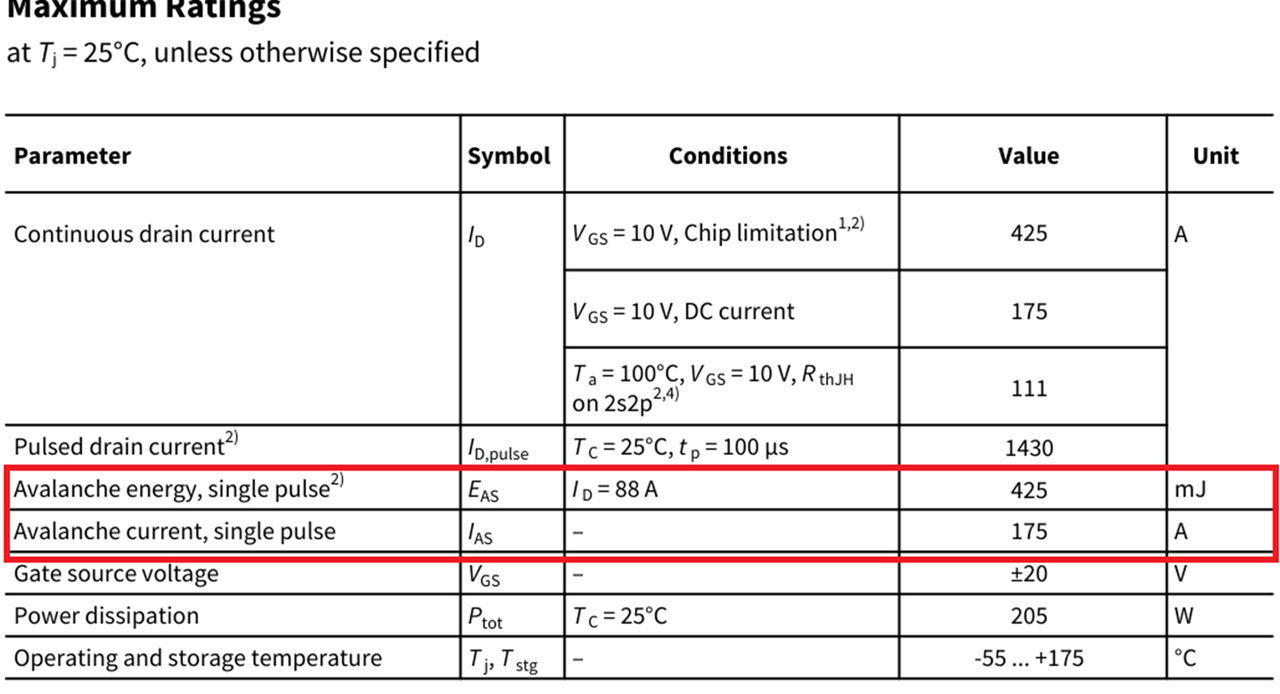

MOSFET 的雪崩特性包括雪崩电流(IAS 和 IAR)和雪崩能量(EAS 和 EAR)。其中,EAS 表示单次雪崩击穿能量,即器件可以安全吸收的反向雪崩击穿能量的高低;EAR 则表示重复雪崩能量,标定了器件所能承受的反复出现的雪崩击穿能量。这些参数的限制条件通常是以器件的最高允许结温为极限。

MOSFET 在单个脉冲中所能承受的雪崩能量有一个定义的最大值,在特定的一组测试条件下,MOSFET 数据手册中将其指定为 EAS。顾名思义,单脉冲雪崩事件只允许发生一次,特别是在条件接近数据手册中提供的限值时。这是因为这些限值对应于高于 MOSFET Tj,max 的结温,因此重复此类事件会损害 MOSFET 的使用寿命。请记住雪崩不是推荐的操作条件。

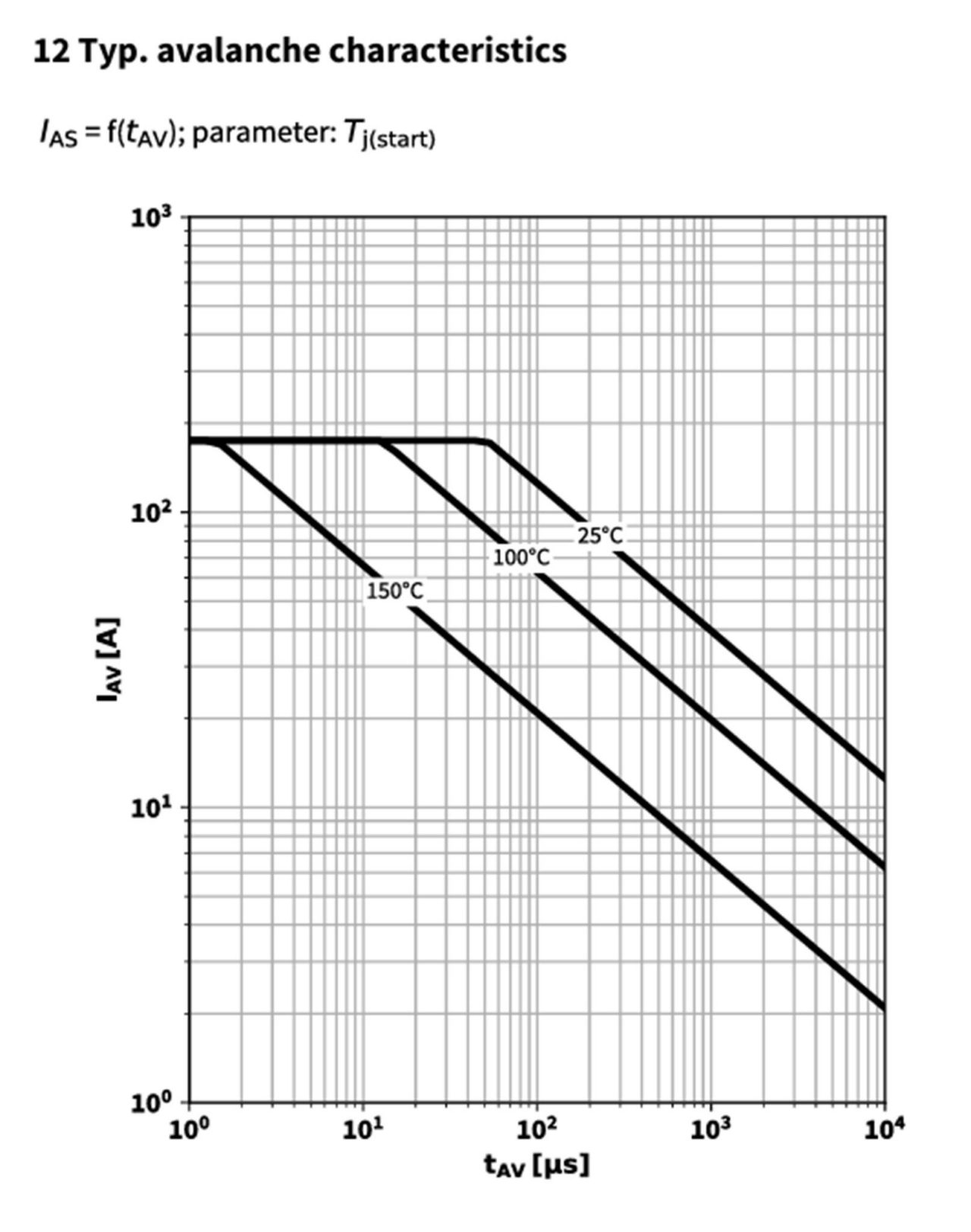

在重复雪崩的情况下,雪崩事件以快速重复频率连续发生,这通常与开关电源转换器等应用电路的开关频率 (fSW) 相同。每个雪崩事件允许的安全雪崩能量远低于单脉冲雪崩。

在大多数重复雪崩情况下,由于每次雪崩事件的能量相对较低,与最坏情况下的单脉冲雪崩相比,硅材料温升可以忽略不计。观察到的 VDS 尖峰仅略微超过 MOSFET V(BR)DSS,(min,25) 额定值,而在高能单脉冲雪崩测试期间记录的振幅为 1.2~1.3 x V(BR)DSS,(min,25)。单次雪崩额定值和重复雪崩额定值之间的相关差异与此类事件引 起的允许 Tj,max 有关。事实上,虽然在单脉冲雪崩中允许结温超过 Tj,max,但对于重复雪崩却不是这样。在重复雪崩中超过 Tj,max 会产生累积效应,这可能会降低器件在其使用寿命内的可靠性,从而导致过早失效。

区分单脉冲和重复雪崩非常重要,因为它们影响正常 MOSFET 特性的方式大不相同。单脉冲雪崩的两种器件失效模式是由高电流(闩锁效应)或高能量(热损坏)引起的。这些失效模式是灾难性的;然而,在重复雪崩情况下,损坏过程是渐进的,通过重复的微损伤非常缓慢地影响器件。即使是低能量雪崩事件也会产生一些热载流子,这些载流子电荷沿着功率 MOSFET 的沟槽氧化物注入。重复雪崩事件会引起电荷积累,这会慢慢损害器件可靠性。这可能导致一段时间后发生现场失效。

(一) 两种雪崩测试系统

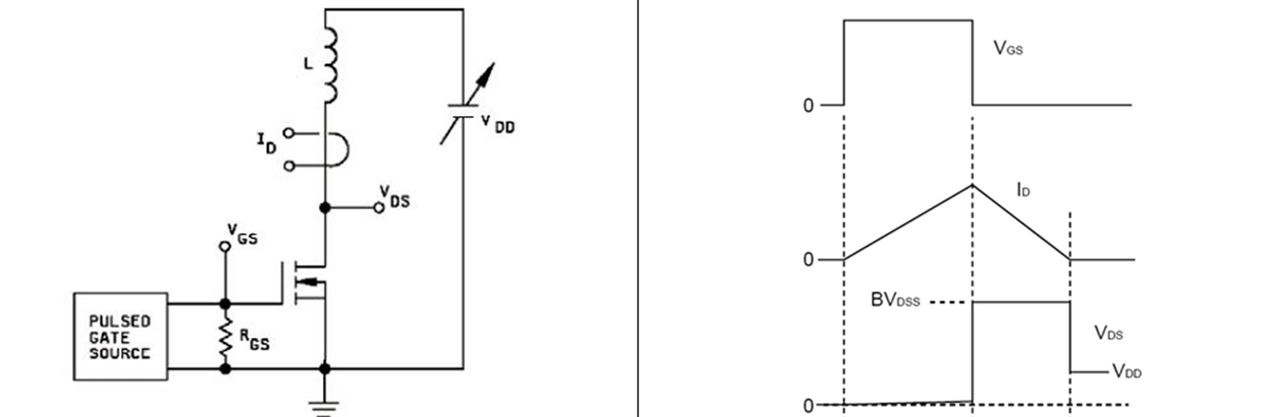

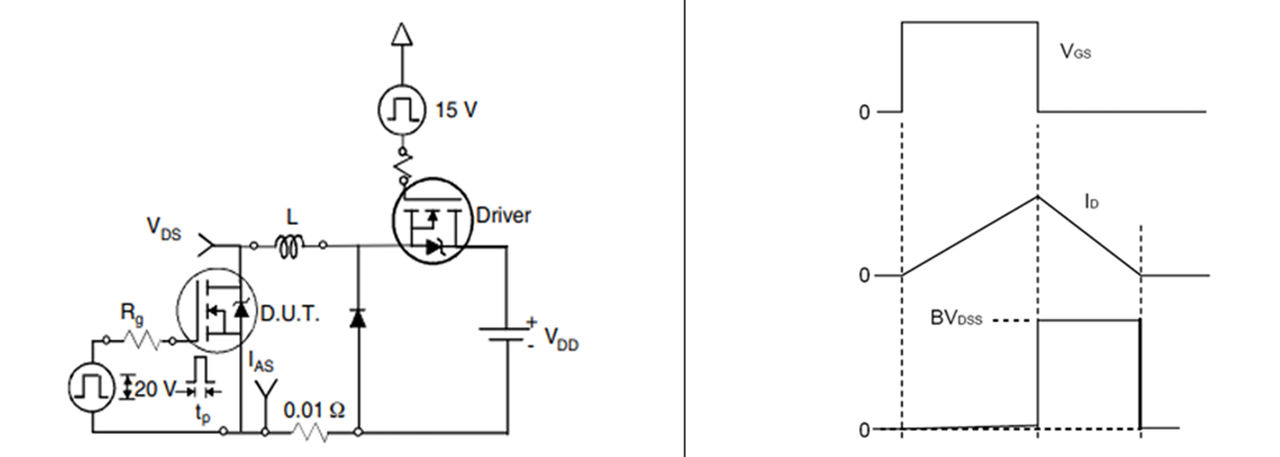

Single pulse unclamped inductive switching(单脉冲非箝位感性负载开关):

如下图(图2)所示的基本原理电路图和测试波形,在感性负载应用(如电感,变压器, 电机等)中使用 MOSFET 时,当 MOSFET 关闭时,由于电感或者电路寄生电感的特性,产生反电动势,该反电动势叠加在输入电压会产生超过 MOSFET 最大额定值 V(BR)DSS 的高电压。

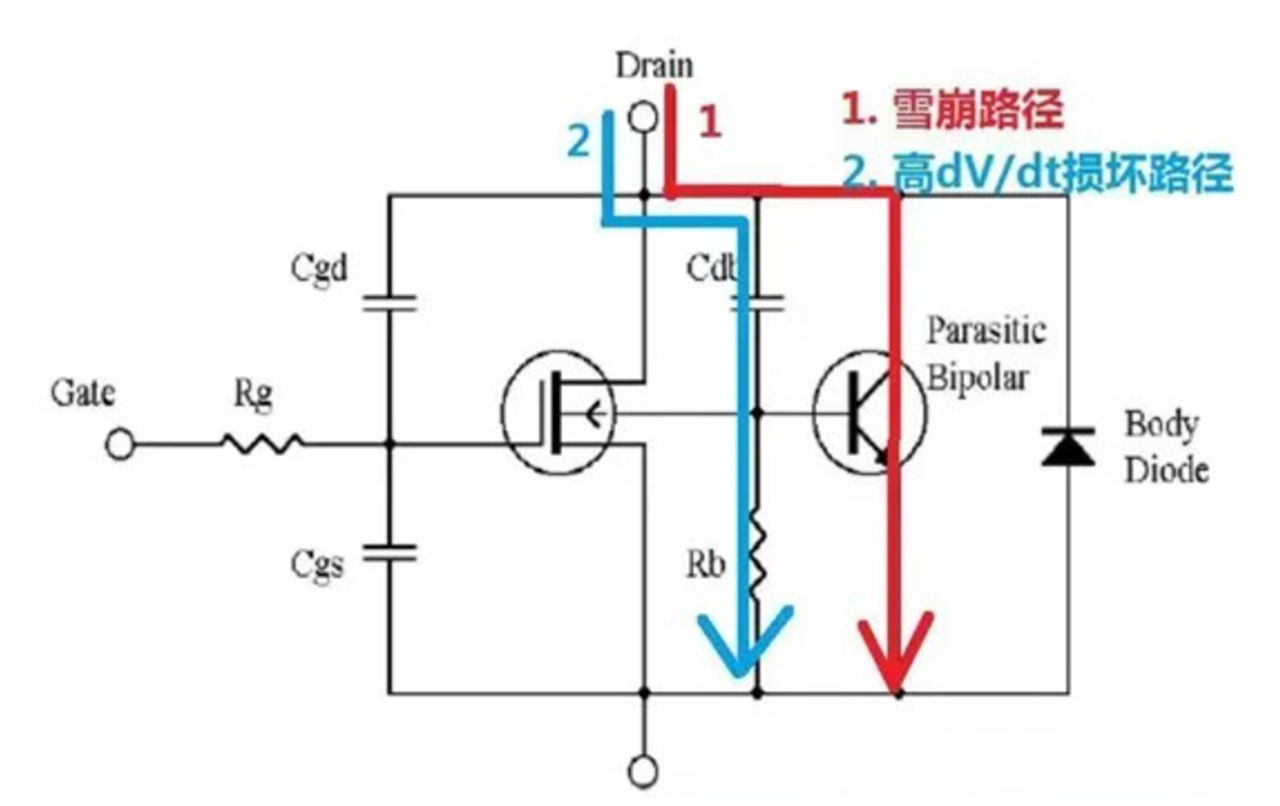

当向 MOSFET 施加高于绝对最大额定值 V(BR)DSS 的电压时,就会发生击穿。当施加高于 V(BR)DSS 的高电场时,自由电子被加速并带有很大的能量,这会导致碰撞电离,从而产生电子-空穴对。这种电子-空穴对呈雪崩式增加的现象称为“雪崩击穿”。在这种雪崩击穿期间,与 MOSFET 内部二极管电流呈反方向流动的电流称为“雪崩电流 IAS”,如图 3 中蓝色路径所示。

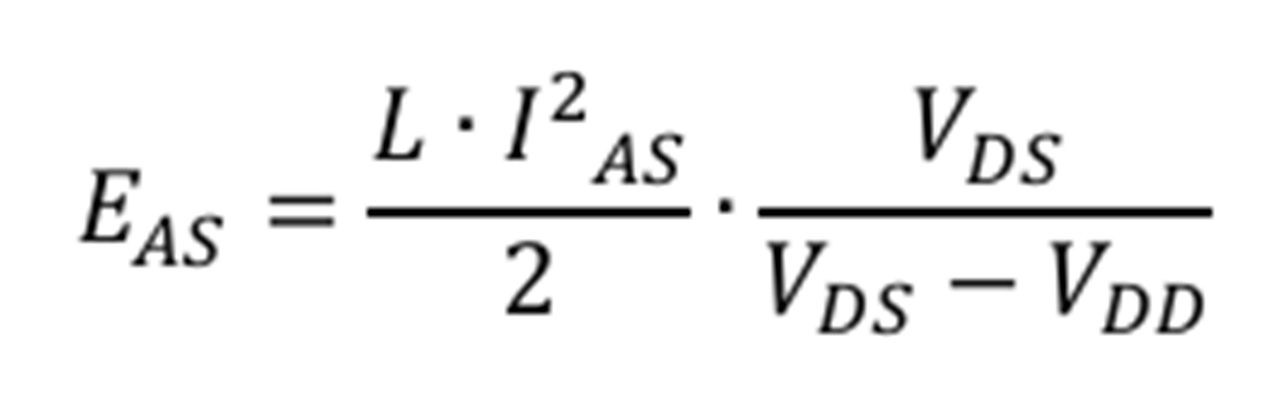

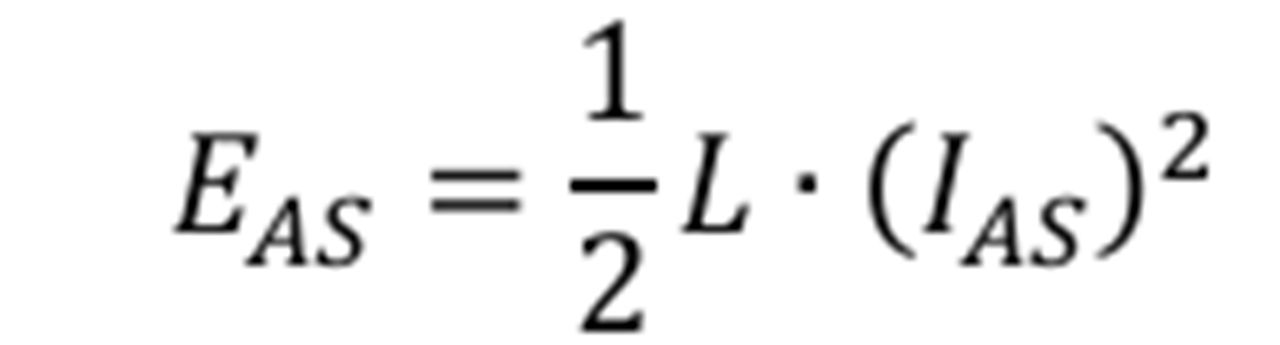

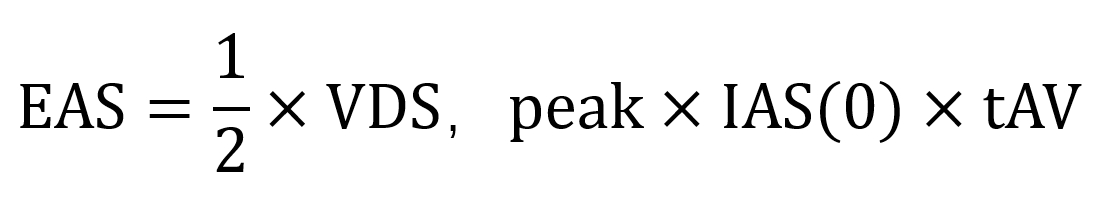

在雪崩击穿期间,不仅会发生由雪崩电流导致寄生三极管误导通而造成的短路和损坏(如前所述),还会发生由传导损耗带来的热量过高造成的损坏。当 MOSFET 处于击穿状态时,会流过雪崩电流,根据图 1 所示波形,在这种状态下,雪崩能量公式为:

这种功率损耗称为“雪崩能量 EAS”。尽管 MOSFET 处于 OFF 状态,电流仍然会几十安到数百安流动,一方面会产生高损耗、高温度,并可能损坏 MOSFET 元胞结构,另一方面过大的雪崩电流会导致 MOSFET 寄生三极管导通,从而使 MOSFET 漏源极在高电压下趋于导通状态,漏源极电流瞬间大幅增加,导致 MOSFET 失效。

Decoupled VDD voltage source(解耦隔离式 VDD 电压源电路):

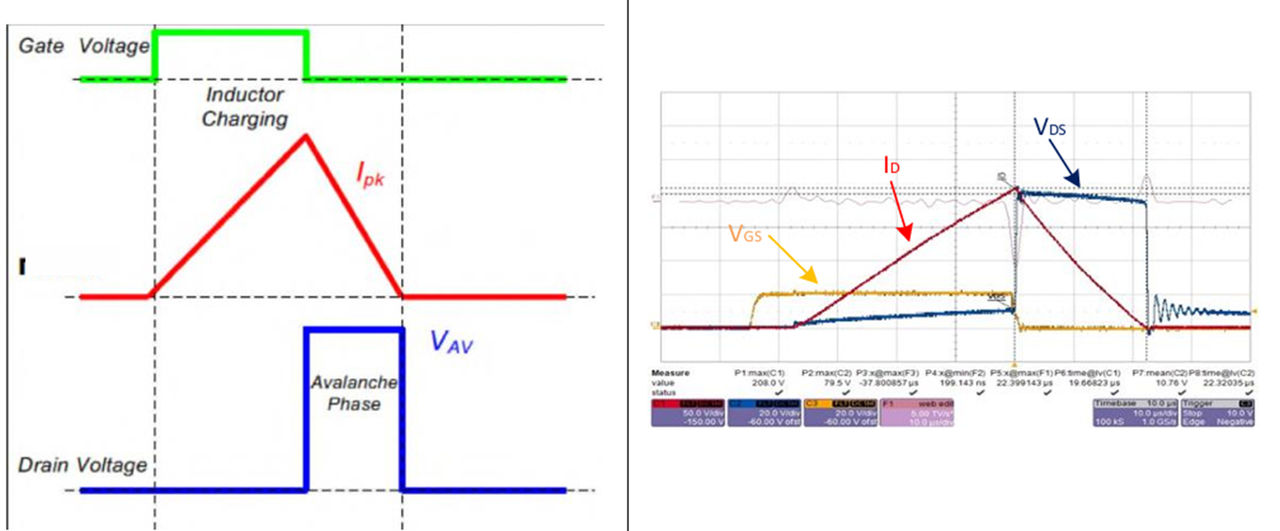

为了突破单脉冲非箝位感性负载开关测试电路的局限性,自 1980s 年以来,已经实现了解耦隔离式 VDD 电压源电路,如下图 (图4) 所示:

这里增加了一个驱动场效应管和再循环二极管,使雪崩时电感两端的压降等于雪崩电压。使用这种电路,能量可以简单地计算为:

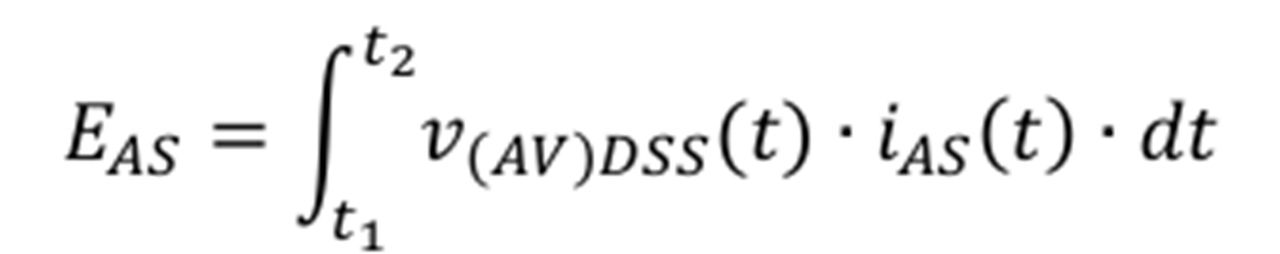

在实际测试中,电压、电流往往不是直线的。如下图(图5)所示:

通过测量器件中的瞬时电压和电流,并按下式积分,可以更好、更准确地读取雪崩能量:

(二) MOS 的 EAS 参数计算

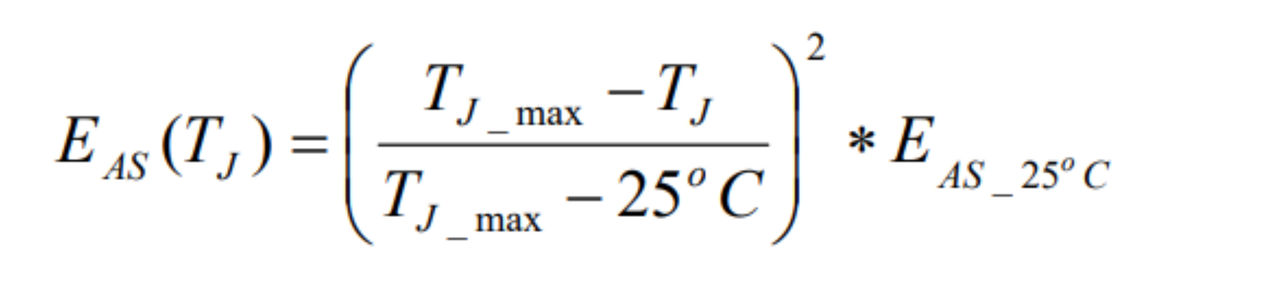

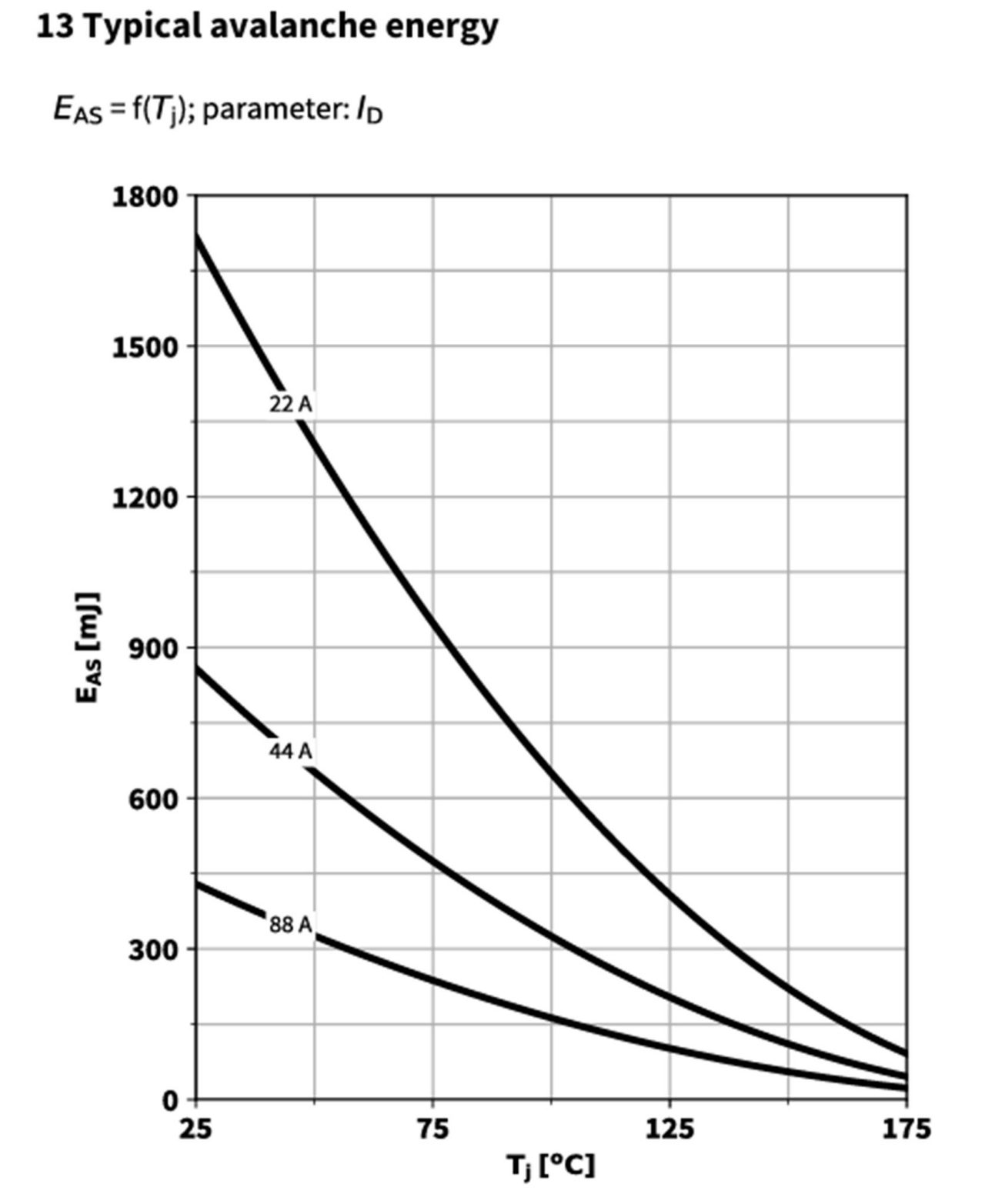

一般 MOS 的 datasheet 只给出了特定条件下的 EAS 参数和曲线,如何计算更多参数条件下的 EAS,满足实际使用的复杂条件是非常重要的。计算更多温度下的 EAS:

计算更多电流下的 EAS:

英飞凌车规 MOS 的 VDS, peak=1.3*V(BR)DSS。

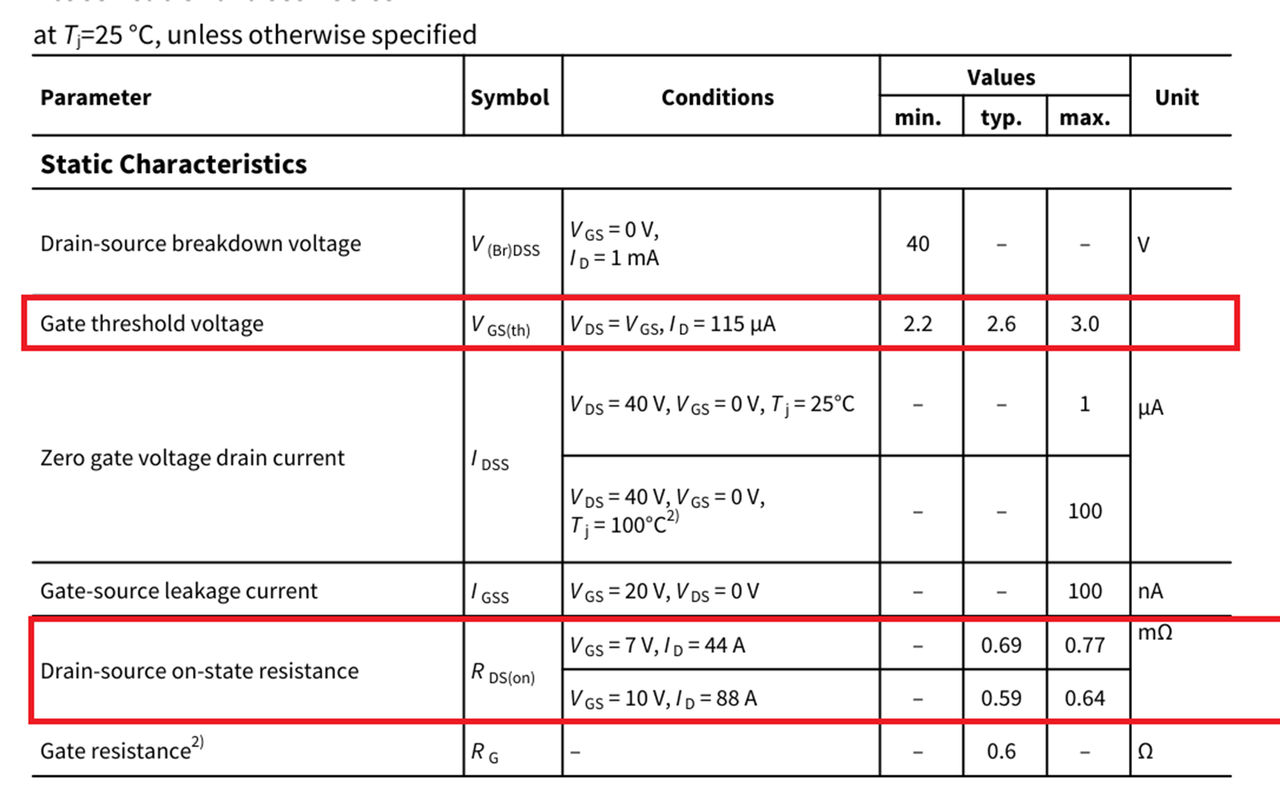

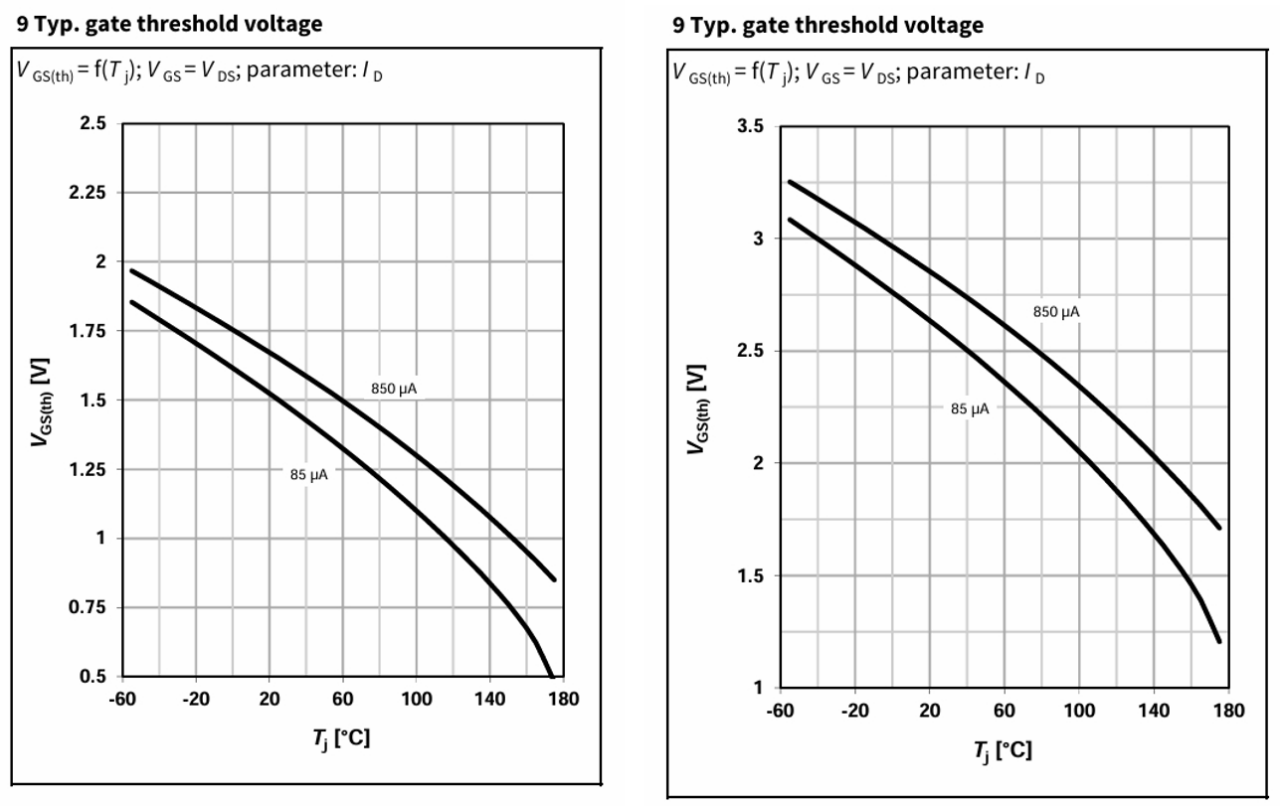

二、VGS(th)

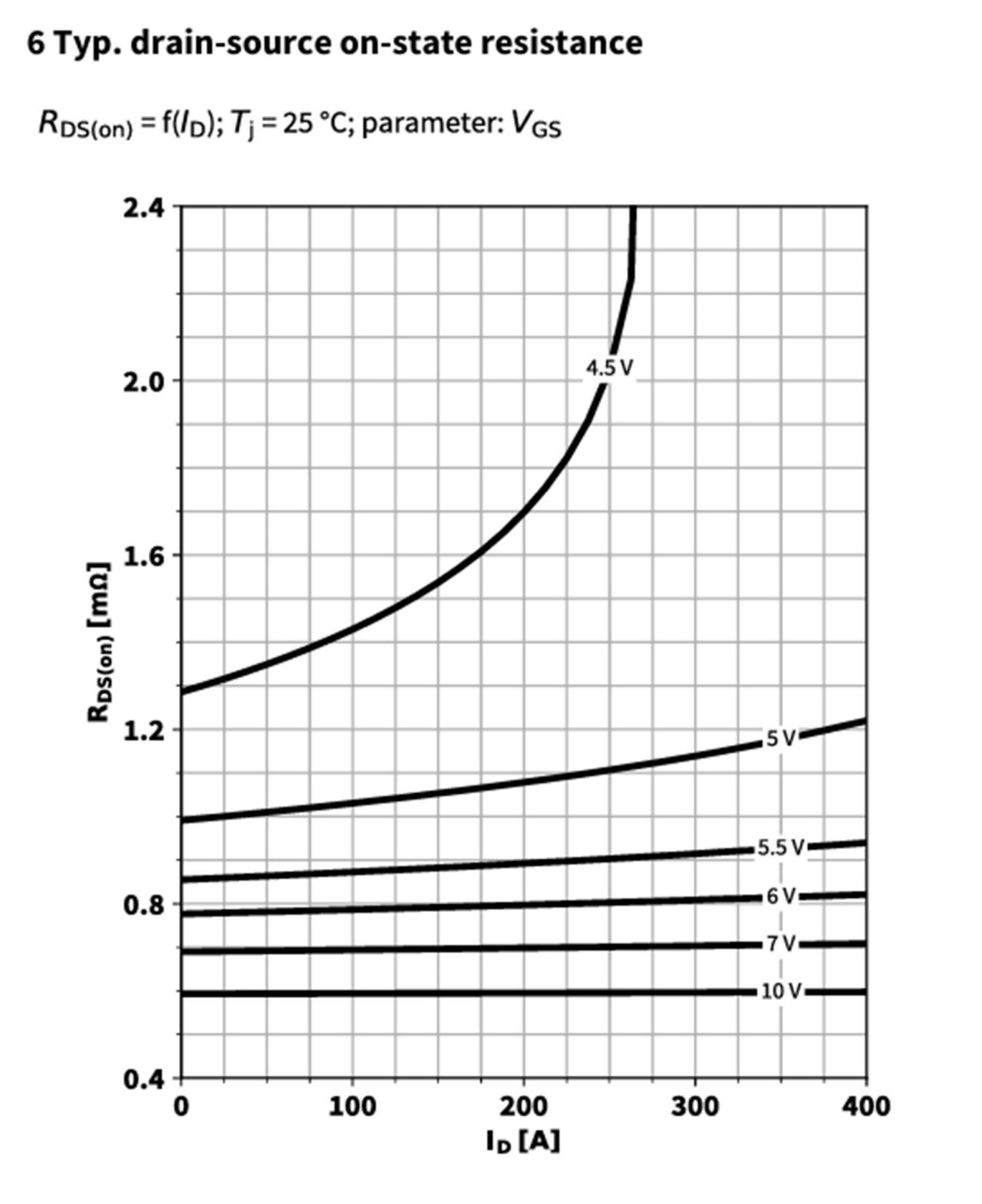

关于 VGS 有两个地方需要特别注意,一个是 VGS(th) 的负温度特性,VGS(th) 会随着温度上升下降,需特别注意在高温下 VGS(th) 误导通的情况,特别是一些浮地驱动的情况。另一个是 VGS 的 RDS-on 的对应曲线,达到 VGS(th) 并不意味着 MOS 就能达到 RDS-on 的标称值,需特别注意 driver 最大输出电压值,避免 MOS 的导通损耗增加。

另外特别注意 Logic Level 的 MOS 的 VGS(th),因本身常温下就比较低,在高温下衰减很容易导致误导通,对 driver 和 layout的要求更高。

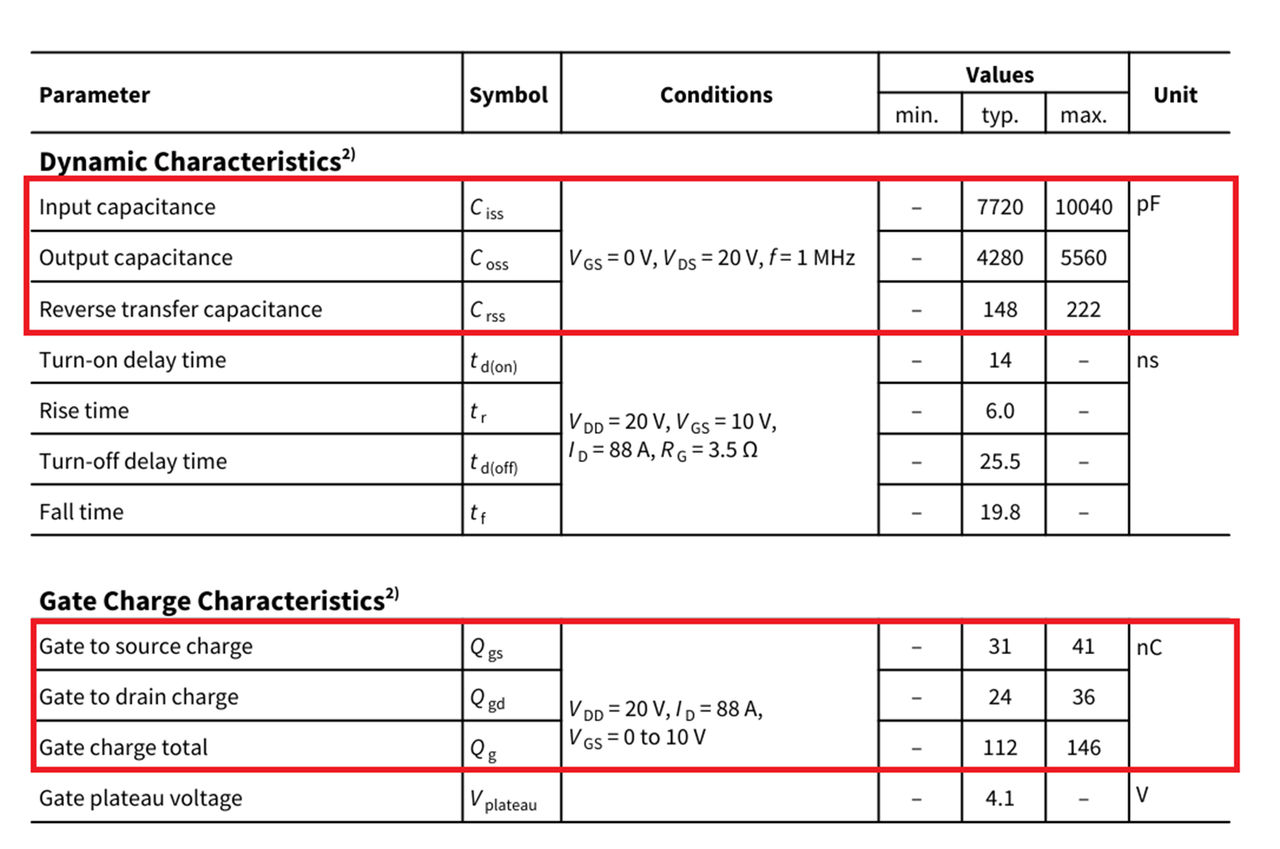

三、Ciss, Coss, Crss和Qg, Qgs, Qgd

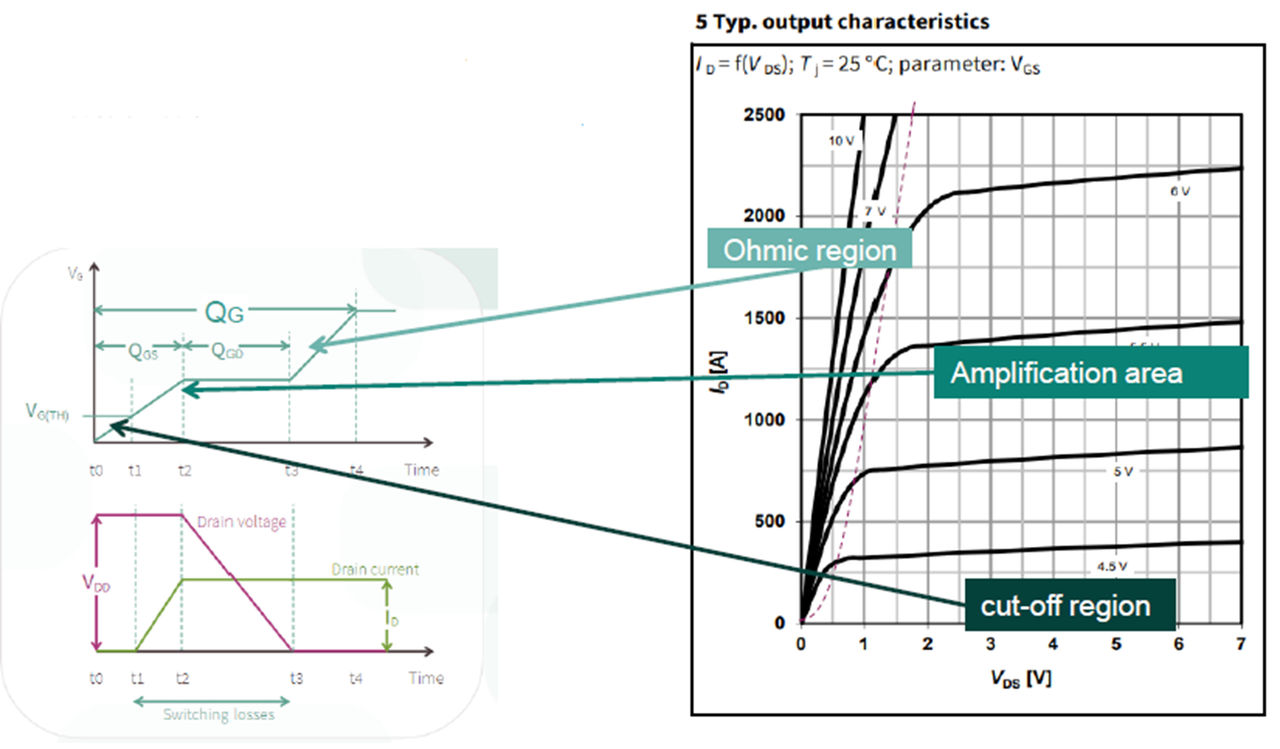

MOS 的 Ciss, Coss, Crss 和 Qg, Qgs, Qgd 将直接决定 MOS 的开启 ON 的 rise time 和 OFF 的 fall time,并影响 EMC 等测试。

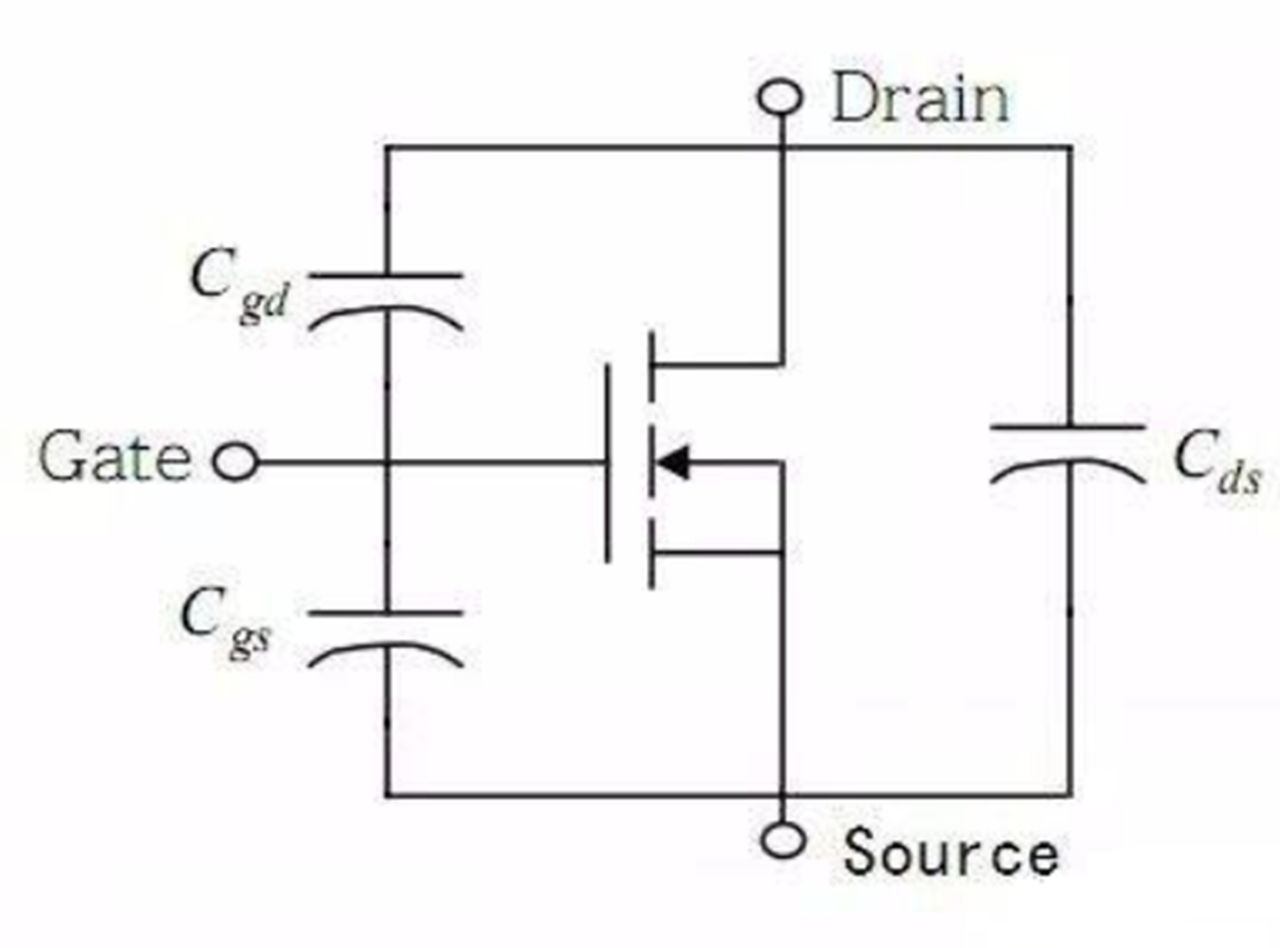

下图(图12)为 MOSFET 寄生电容的等效模型:

各电容之间的关系为:Ciss=Cgd+Cgs, Coss=Cgd+Cds, Crss=Cgd

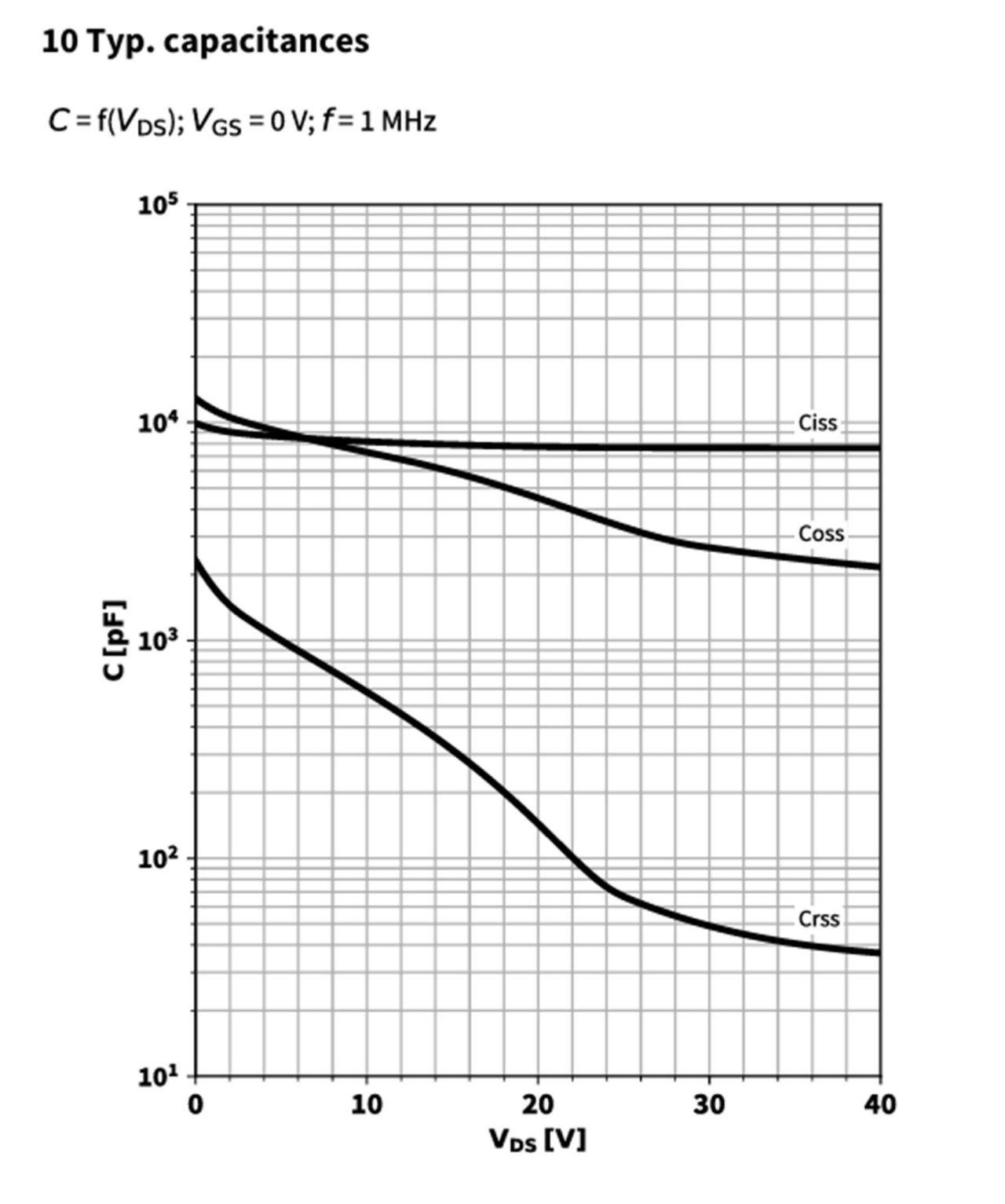

需要特别注意的是,Ciss, Coss, Crss 的容值都是随着 VDS 电压改变而改变的。

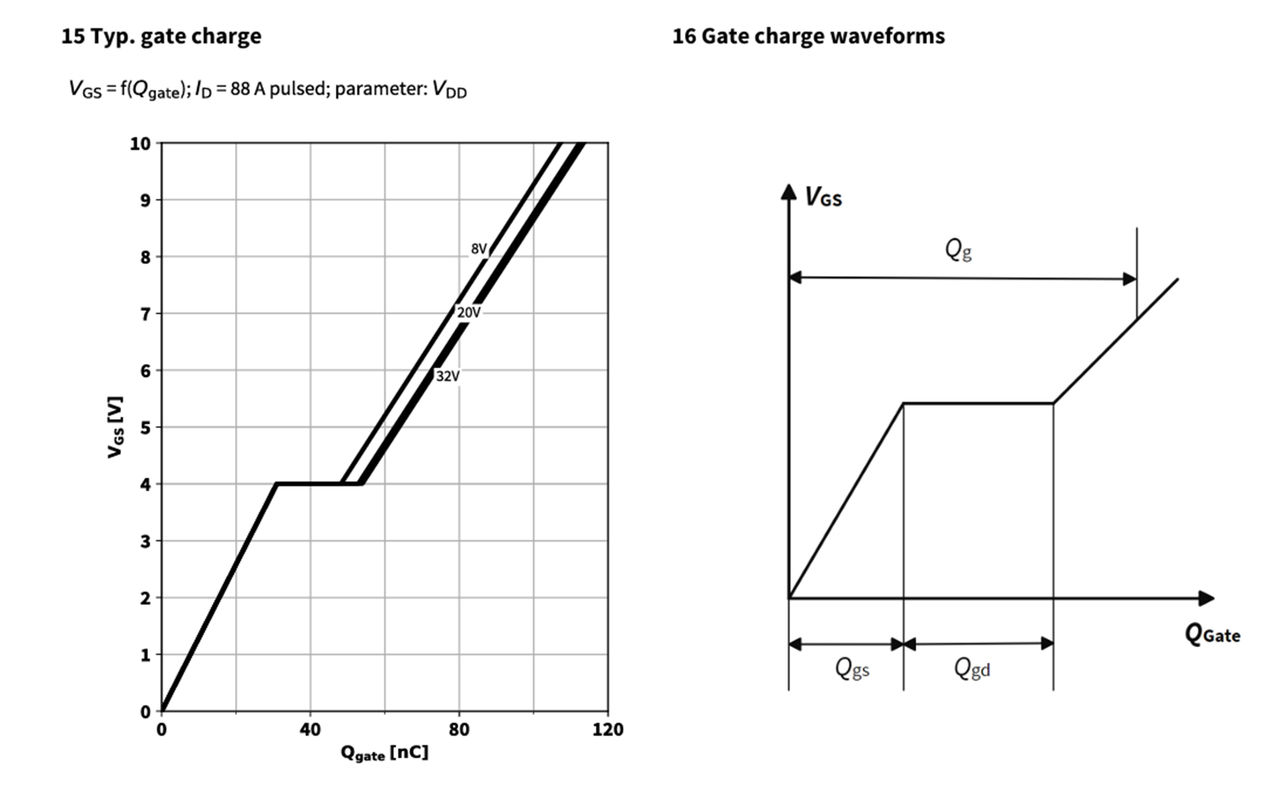

从 MOS Qg 曲线(图15)可以观察到两个重要现象:

- Qg 并不等于 Qgs+Qgd

- Vgs 高,Qg 大,而 Qg 大,驱动损耗大

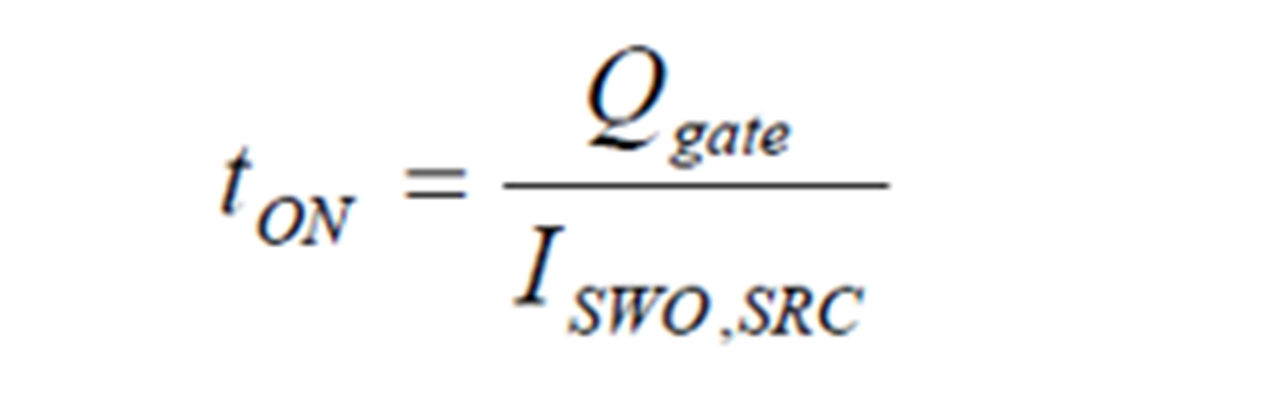

由此计算 tON rise 和 tOFF fall 时间,公式如下:

任何应用、架构下,谨慎计算 MOS 的 tON rise 和 tOFF fall,以及对应的开关损耗,避免开关损耗过大,MOS 热受损。特别是 thermal instability 平衡点以下的时刻。

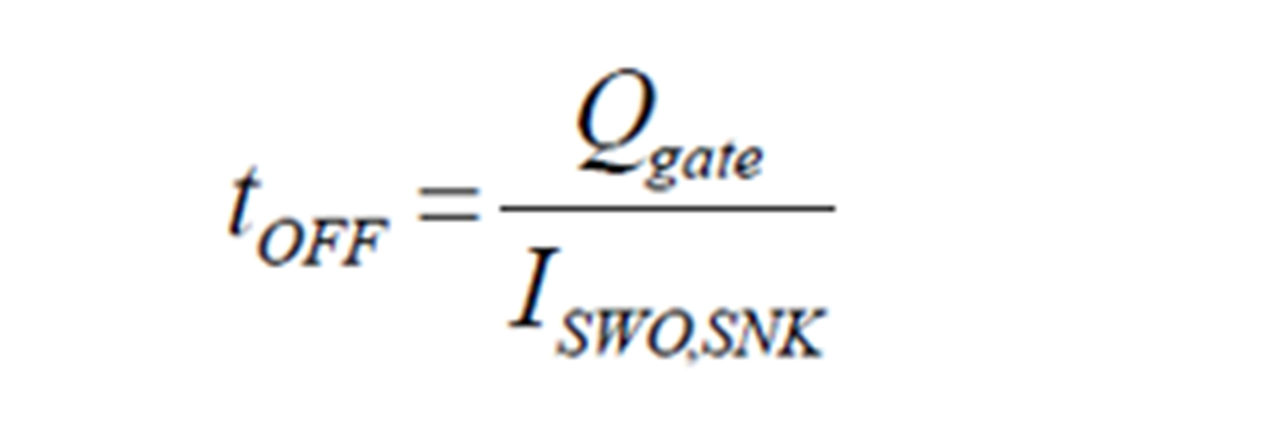

四、Reverse Diode(体二极管)

Reverse Diode 对于半桥、全桥、电机、续流等需要用到二极管的应用场景中,是非常关键的参数。一个强建的体二极管,对于系统的可靠性是非常重要的。

与其他 p-n 结二极管一样,MOSFET 体二极管具有少数载流子反向恢复,因此具有一定的反向恢复时间。当二极管在承载正向电流的同时反向偏置时,就会发生反向恢复现象。反向恢复在数据表中的特征是时间 trr 和在一组指定条件下测试的反向恢复电荷 Qrr。

在实际应用中,体二极管的压降、Reverse recovery time 将直接影响 EMC、效率等结果。选择合适的体二极管,往往在部分应用中具有有决定性的作用。

五、热阻

(一) 热特性基础

在通常条件下,热量的传递通过传导、对流、辐射三种方式进行。

- 传导是通过物体的接触,将热流从高温向低温传递,导热率越好的物体则导热性能越好,一般来说金属导热性能最好;

- 对流是通过物体的流动将热流带走,液体和气体的流速越快,则带走的热量越多;

- 辐射不需要具体的中间媒介,直接将热量发送出去,真空中效果更好。

三种传热方式的基本定律为:

- 热传导的 Fourier 定律:𝑄=𝜀∁(∆𝑇)/𝛿

- 热对流的 Newton 定律:𝑄=𝛼∁(∆𝑇)

- 热辐射的定律:𝑄=5.67𝑒−8𝛽∁(𝑇ℎ4−𝑇𝑐4)

其中 𝜀, 𝛼, 𝛽 为导热系数,换热系数和发射率。C 为换热面积。

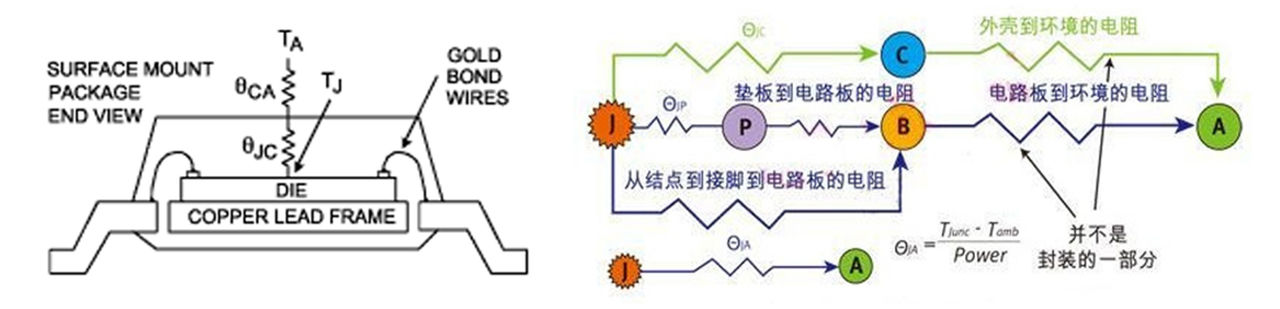

半导体器件热量主要是通过三个路径散发出去:封装顶部到空气,封装底部到电路板和封装引脚到电路板。电子器件散热中最常用的,也是最重要的一个参数就是热阻(Thermal Resistance)。热阻是描述物质热传导特性的一个重要指标。

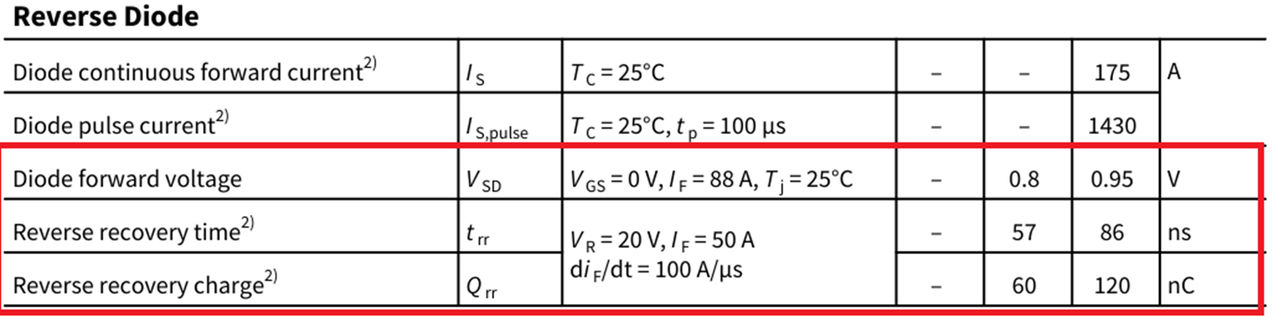

关于英飞凌的 datasheet 中标明的所有热阻都是在限定条件下测得的,实际可以通过很多外部设计来优化热阻。

MOS 的热阻模型如下图(图18)所示:

从热阻模型可以看出各种热阻的关系如下:

Rth-JA = Rth-JC + Rth-CA

Rth-JH = Rth-JC + Rth-CH

Rth-JC:Junction-to-case thermal resistance

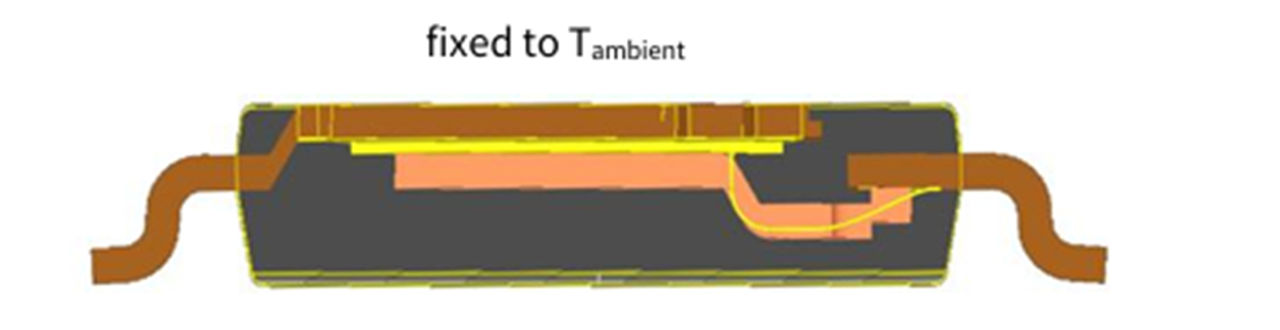

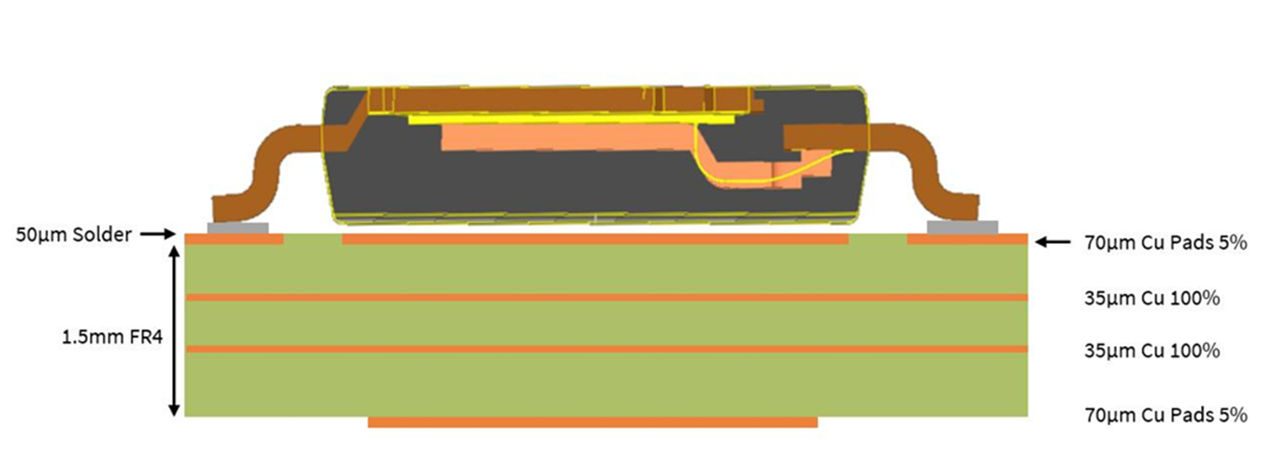

结至外壳热阻指标是设计用于在连接散热器时估算封装的热性能,是 MOS 的运行部分到最近接芯片安装区域的封装(外壳)外表面的热阻。英飞凌的 Rth-JC 测试条件如下图(图19)所示。Package 的 TOP 外露在环温中,另一侧固定在绝热边界条件中测试。

Rth-JA:Junction-to-ambient thermal resistance

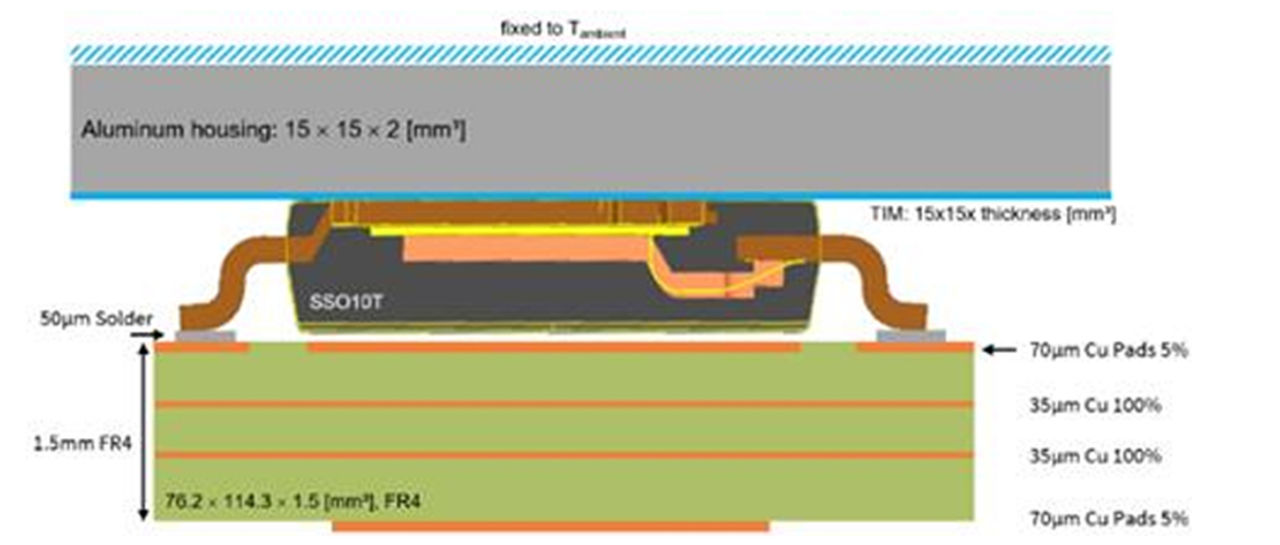

结至环境热阻 Rth-JA 是最常见的热指标,也是最常误用的指标。Rth-JA 是安装在特定测试板上的 IC 封装散热性能的度量。Rth-JA的目的是给出一个指标,通过该指标可以比较封装的相对热性能。英飞凌的 Rth-JA 测试条件如下:

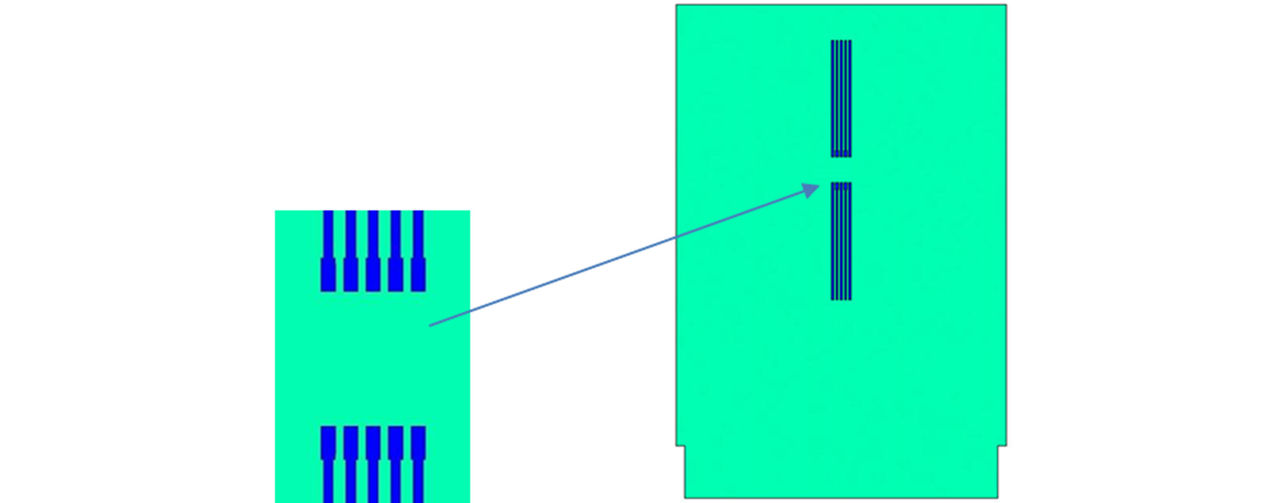

- 使用 JEDEC (Joint Electron Device Engineering Council) 板用于热评估。PCB 结构根据 JEDEC 标准 2s2p,没有热过孔,如图 20 所示

- PCB 尺寸- 74*116*1.5 mm

- 自然对流

Rth-JH:Junction-to-ambient thermal resistance, metal housing

英飞凌增加了参考金属散热片的热阻,供做热设计的参考。测试条件如下:

- 使用 JEDEC (Joint Electron Device Engineering Council) 板用于热评估。PCB 结构根据 JEDEC 标准 2s2p,没有热过孔,如图 22 所示

- PCB 尺寸- 74*116*1.5 mm

- 自然对流

- 金属外壳顶部的温度固定在 Tambient,85°C

- 散热器 71x110x2 mm,通过 TIM 连接,3.3 W/(m*K),厚度 400µm

从以上可知,Rth-JA 是一个并不专属于封装的可变函数,它也是诸如已安装器件上印刷电路板 (PCB) 的设计和布局布线等很多其他系统级特性的函数。实际上,测试板是一个焊接在器件引线上的散热器。 更改测试板的设计或配置也会改变散热器的效率,并因此改变测得的 Rth-JA。

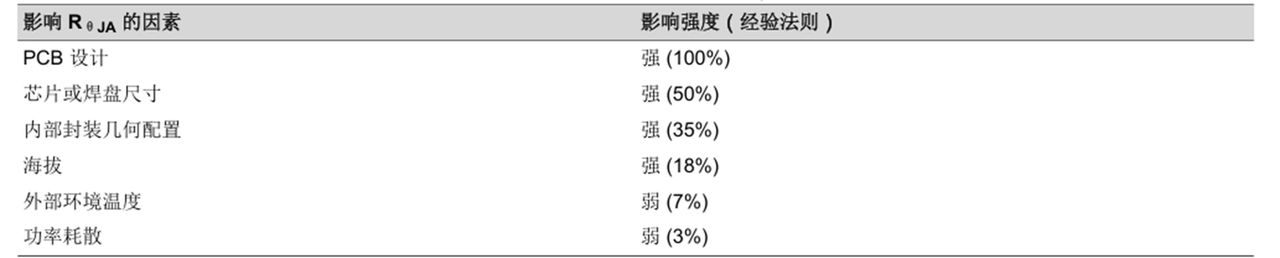

事实上,在静止空气中执行 JEDEC 定义的 Rth-JA 测量时,芯片产生的功率几乎有 70% 至 95% 从测试板耗散,而不是从封装的表面散发。下表列出了在所有材料保持不变时,会影响给定封装外形的 Rth-JA 的因素。第一列列出了因素,而第二列给出了凭经验法则估算出的影响程度。

鉴于 Rth-JA 不仅仅取决于封装本身的特性,还取决于封装、PCB 和其他环境因素的特性这一事实,所以最好将它用于比较不同公司、不同封装之间的热性能。

六、总结

本文深入解读了 MOSFET 数据手册中的另外五个关键参数:雪崩特性、VGS(th)、寄生电容与栅极电荷、体二极管以及热阻。下一篇将结合汽车电子中的典型应用场景——DC/DC转换器、PDU/SPDU/efuse、BLDC 电机驱动,分析这些关键参数在实际设计中的选型要点和注意事项,帮助工程师将参数知识转化为实际应用能力。

欲了解关于更多英飞凌相关方案或技术信息,请与骏龙科技当地的办事处联系或点击下方「联系我们」,提交您的需求,骏龙科技公司愿意为您提供更详细的技术解答。

相关阅读

更多信息: