瑞萨 RL78/F13 MCU 引脚冲突和功能映射的 CS+ 配置修改经验

本文基于实际项目经验,详细介绍了在瑞萨 RL78/F13 微控制器中,如何通过 CS+ 开发环境重新配置已占用引脚功能,解决外设功能与普通 I/O 口之间的资源冲突问题。

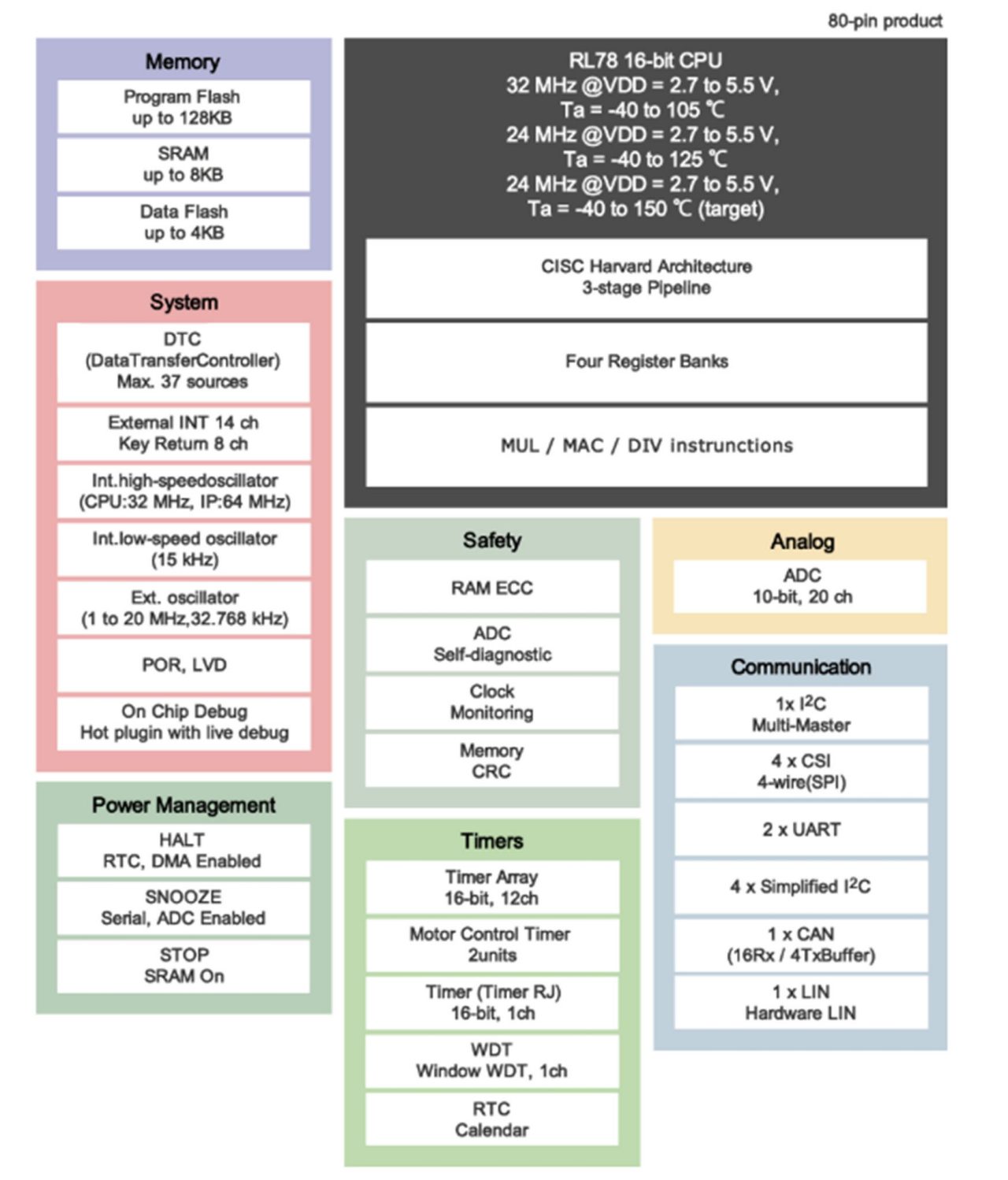

一、产品介绍

瑞萨 RL78/F13 是一款适用于汽车应用的低功耗 MCU,为 78K0R 和 R8C 的后续产品,提供 20 至 80 引脚、16KB 至 128KB 闪存阵容,可实现业界领先的低消耗电流水平。该器件内置了用于汽车接口的 CAN 模块和 LIN 模块,除了功能安全功能外,还增加了 RAM ECC 功能、PLL 锁定功能、端口输出状态监控、堆栈溢出检测、专用 WDT 振荡器等。 因为可以构建高度可靠的系统,所以这些微控制器可用于工业应用及汽车应用。

二、项目背景

在项目的实际开发过程中,往往会出现新项目是基于旧项目扩展和更改的情况,有时会发生新项目比旧项目需要更多的 MCU 资源的情况。比如需要额外增加一些管脚来作为 ADC,或者 GPIO 等功能,这个过程会涉及到对于 MCU 管脚的重新管理等操作。以下是本次介绍项目的一些开发背景:

- 使用芯片:瑞萨 RL78/ F13:64-pin 16 bit MCU

- 使用 IDE: 瑞萨 CS+

- 使用接口:LIN-BUS、CAN-BUS、ADC、PWM、GPIO

- 问题:由于目前项目设计正好 64 个 pin 都占满,新的项目需要新增加一个 I/O 口,但因资源不足,希望可以在不换 MCU 的前提下,关闭一个既有的不那么重要的外设口,从而作为一个新的普通 I/O 口来使用。

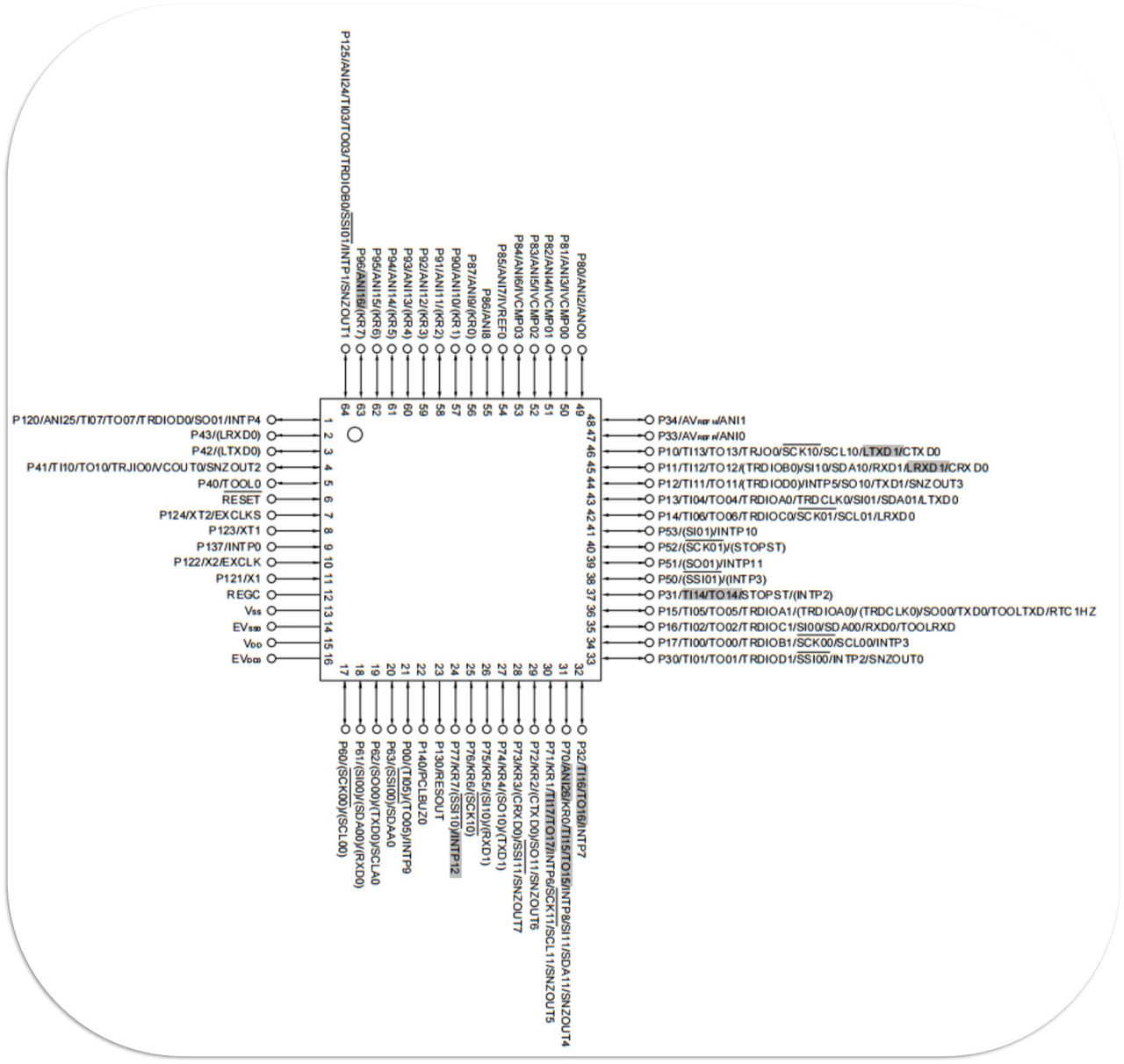

64-pin F13 产品 pin 脚功能一览

如下图 (图2) 为 64-pin 的 F13 的管脚和功能分布情况 (图源瑞萨 F13/F14 硬件手册):

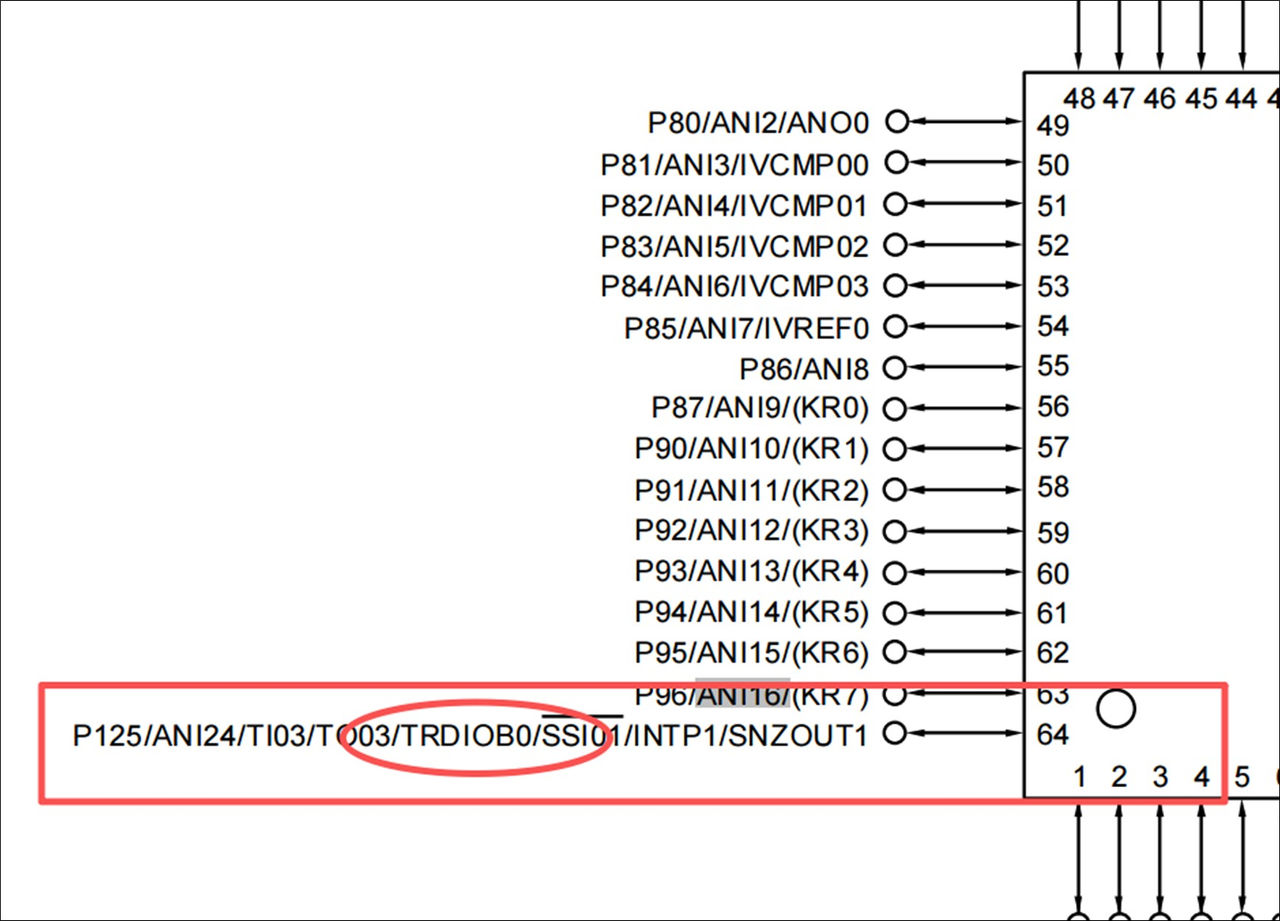

项目中需要把位于第 64 pin 的引脚抽出,重新配置为普通输出 output I/O 使用。而目前的 CS+ 设定是基于旧有工程,该引脚已被作为 TRDIOB0 (一种高性能定时器外设模板) 外设功能占用。在将 TRDIOB0 切换到普通 I/O 的过程中出现了问题,需要了解具体的配置方法,后面会详细介绍。

CS+ Pin assignment setting 界面介绍

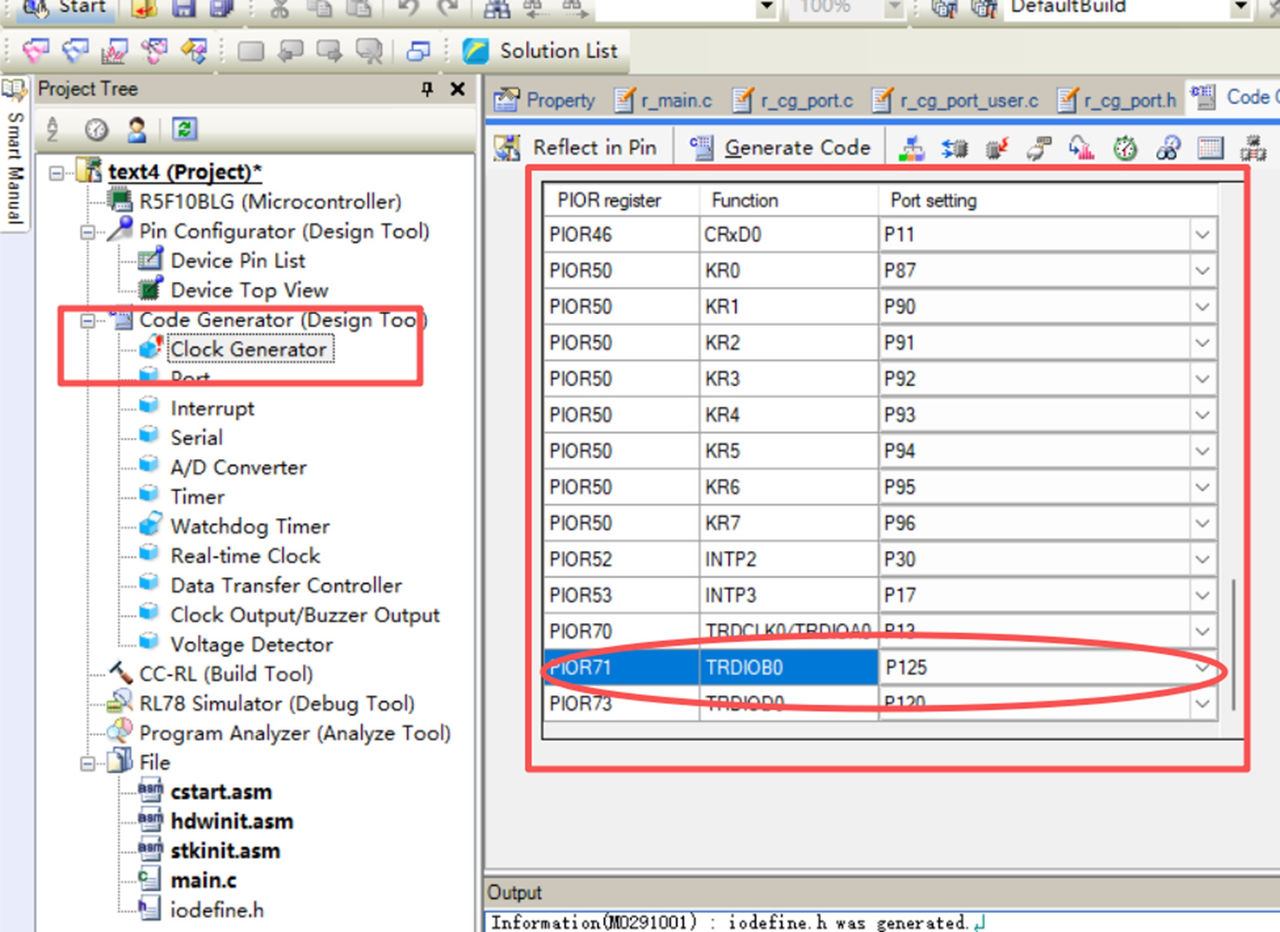

在创建新工程时,clock generator 模块通常会显示一个红色感叹号,提示需要先在 Pin assignment setting 界面完成 pin 功能配置才可以进行后续操作。

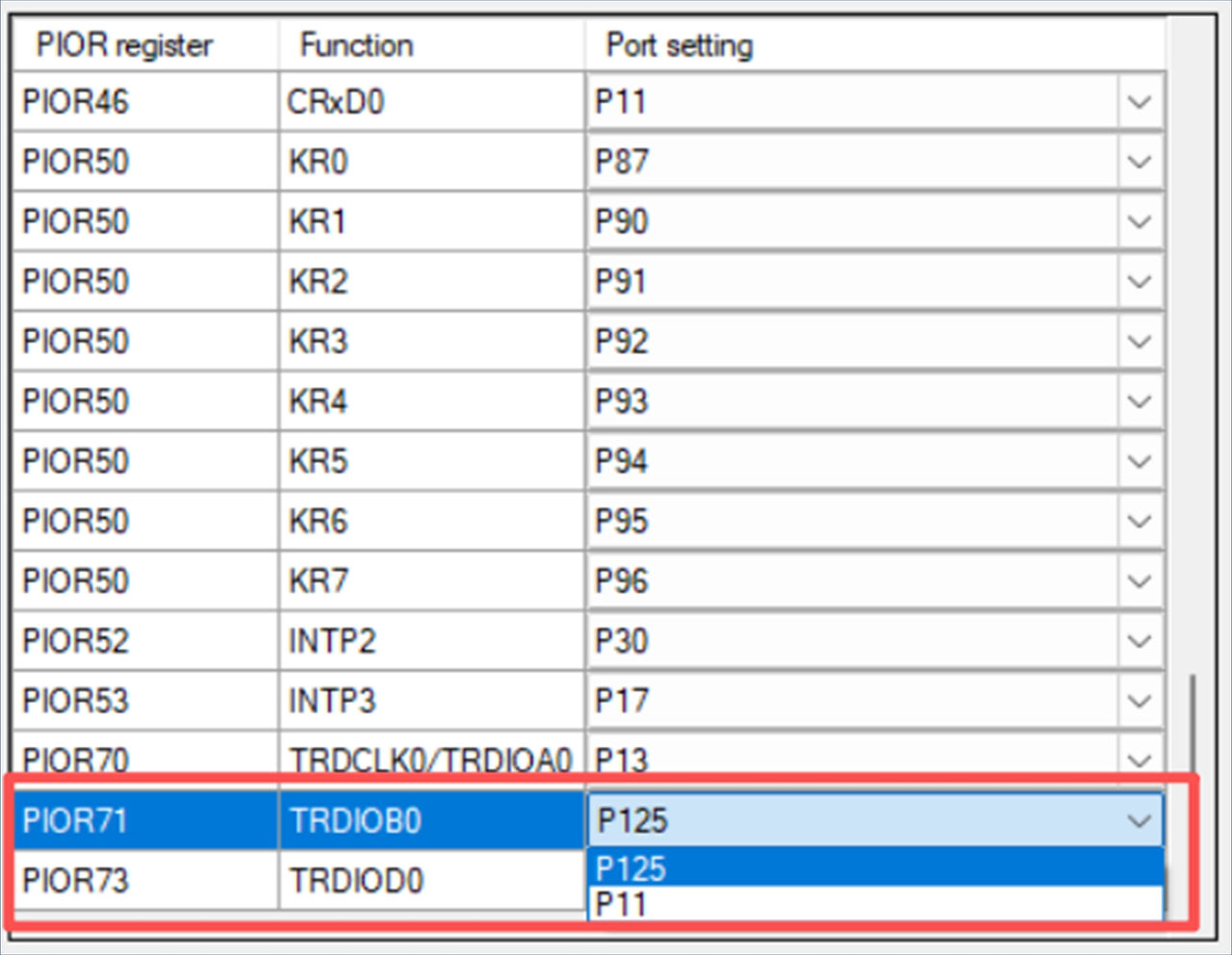

在 Pin assignment setting 界面中,PIOR 是端口输入输出重定向寄存器,Fuction 是对应的功能,在Port setting 里可以选择对应的端口号。通过 Pin assignment setting 界面,可以把需要的管脚功能映射到后面 Port setting 中具体的端口上。如下图 (图4) 例子中 PIOR71 这行,TRDIOB0 定时器外设的功能被映射到了 P125 (对应硬件 pin 脚号为 64) 这个端口上。

选择完功能后,点击上方的【fixsettings】按钮即可完成功能映射。一些特定功能不存在复用情况的管脚会直接被设置并分配好,比如 reset 管脚等。

三、常见配置疑问与解答

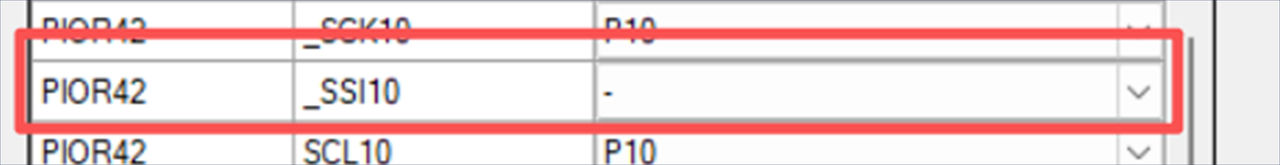

为何有的外设功能可以【-】,有的必须得映射一个 PORT?

如下图 (图5) 所示,有些功能 (如 _SSI10) 可以选择不映射,直接【-】掉。而在下图 (图6) 例子 PIOR71 中的 TRDIOB0 功能,却只能选择 P125 和 P11,无法【-】掉。这是因为在 CS+ 配置中,有些特殊引脚需要强制绑定一个 I/O,如果不用这个功能,后面需要去关闭,不然无法作为普通 I/O 来使用。

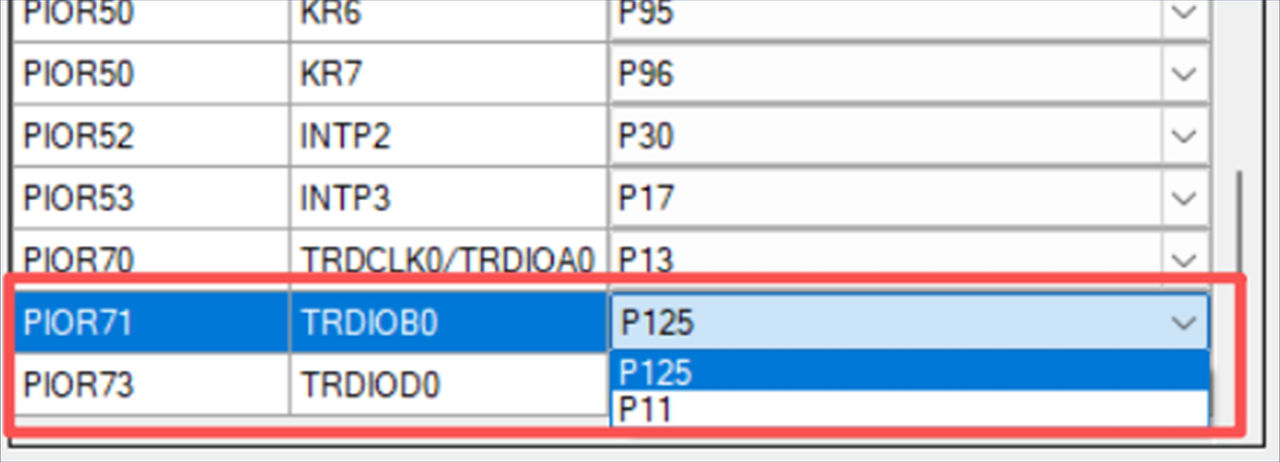

可否通过多个功能映射到一个 PORT 上,从而实现多个功能?

如下图 (图7) 所示,PIOR46 和 PIOR71 都映射给 P11,但这并不代表 P11 可以同时兼具两个功能来使用。图片配置界面只是单纯把功能映射上去,这两个功能都作为候补选手,映射完后,可以选择其中之一进行配置并使用。也就是说,在实际使用时,一个 pin 脚只能选择一个功能来使用,选了作为 CRxD0 这个功能,就没有办法使用 TRDIOB0 这个功能了。

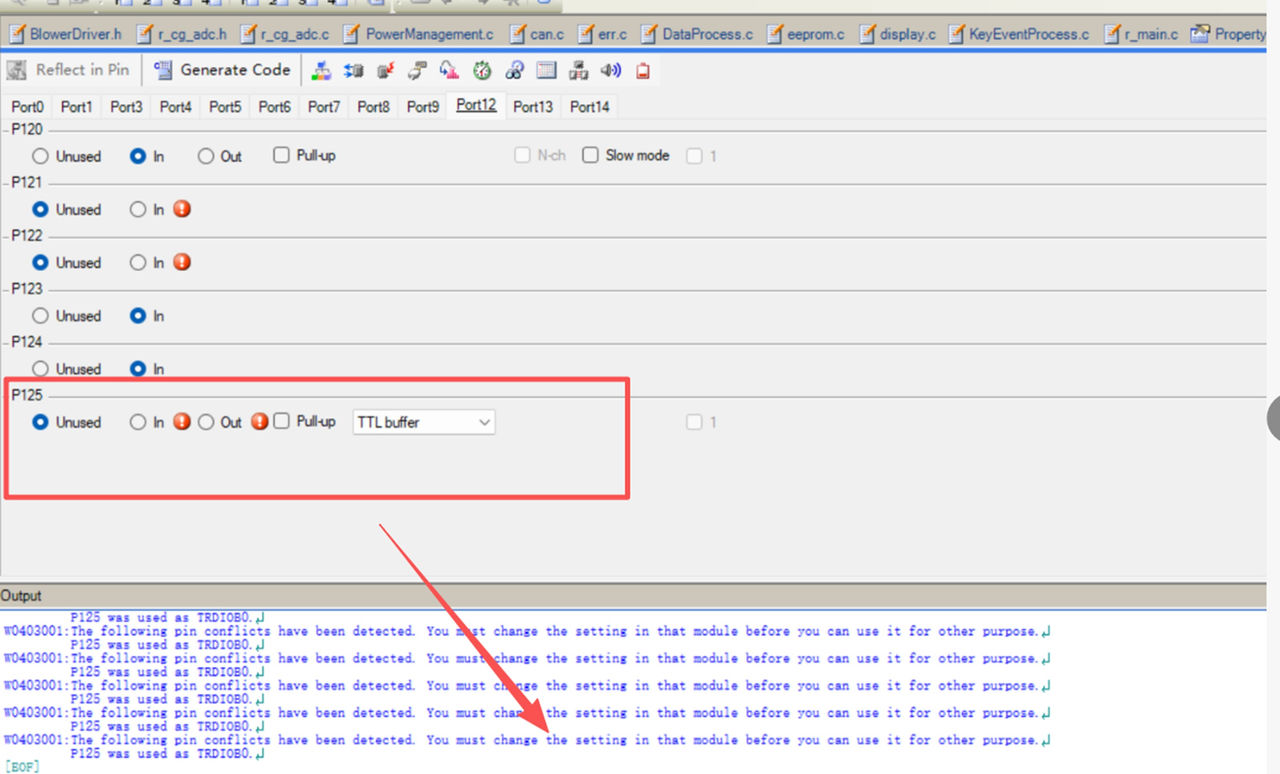

为什么 PORT 界面无法设置?并且有很多红色感叹号?

下图 (图8) 为 PORT 的配置界面,点击工程中的【PORT】即可进入该页面,P125 所在的 port 组是 PORT12 这一栏目 (P12 端口的第 5 个),一般在新工程建立的时候,该界面是可以直接进行配置的。

而图中的 P125 的描述情况是,已被选中【Unused】,即未使用该 I/O。后者之所以会出现红色叹号,是因为 CS+ 检测到该端口被其他功能占用,蓝色提示栏已指出,即 TRDIOB0 外设,所以需要先去【Timer】模块里取消该功能。

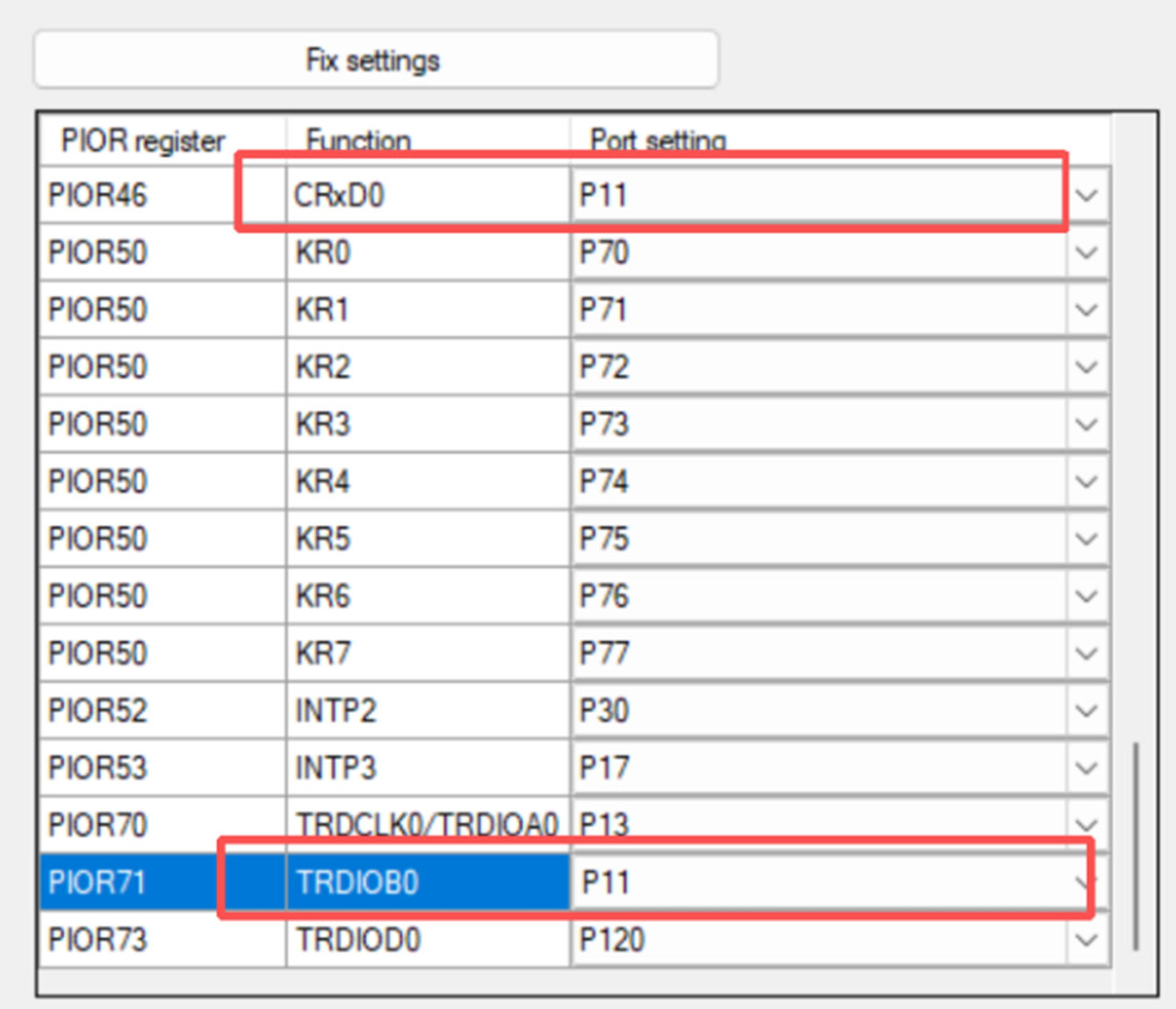

如何具体实现取消 TRDIOB0 并修改为普通 I/O?

根据下图 (图9) 所示界面来看,目前 TRDIOB0 分配给了 P125,想取消 TRDIOB0 功能,根据二选一原则,那只能选择分配给 P11,但是 P11已被用作 CAN 的输出接口,这时直接修改代码会很麻烦。

更快捷的方法是,在此界面选择先选择映射到 P125,后续再在 PORT 界面中设置作为只用普通 I/O 这个功能即可。目前的工程就是已映射到 P125,并且已开启了该 TRDIOB0 这个定时器功能,我们需要将已被占用的 TRDIOB0 功能改为普通 I/O。下面介绍具体操作步骤:

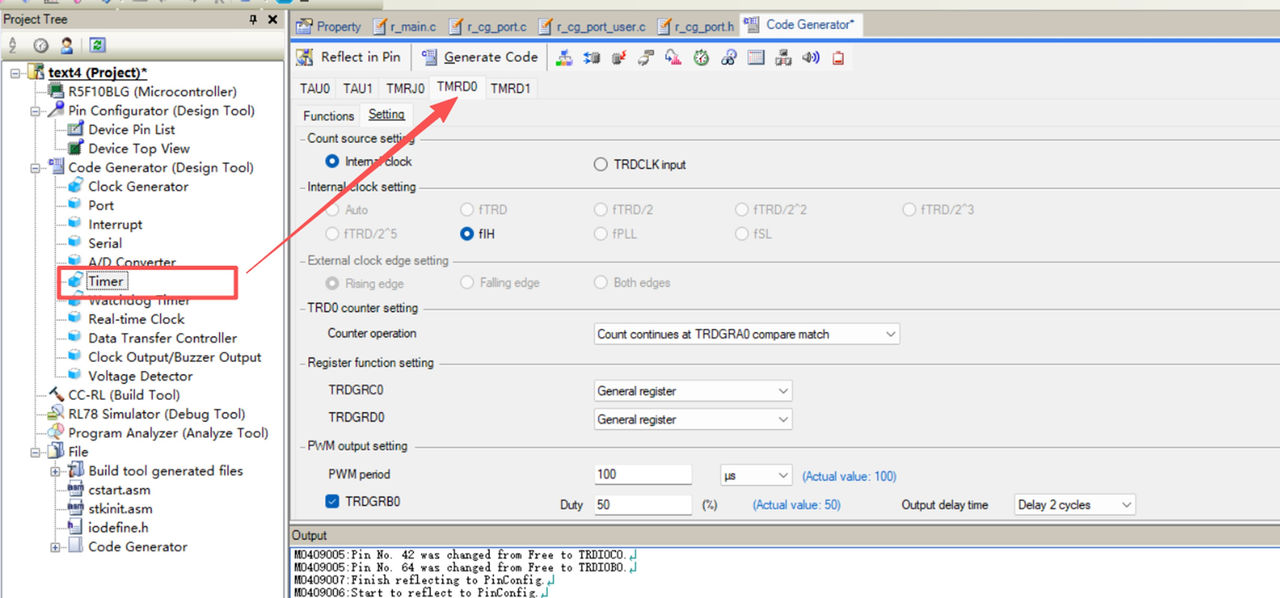

1、找到配置选项

打开【Timer】界面,选择 TMRD0 (因为 TRDIOB0 属于 TMRD0),如下图 (图10) 所示:

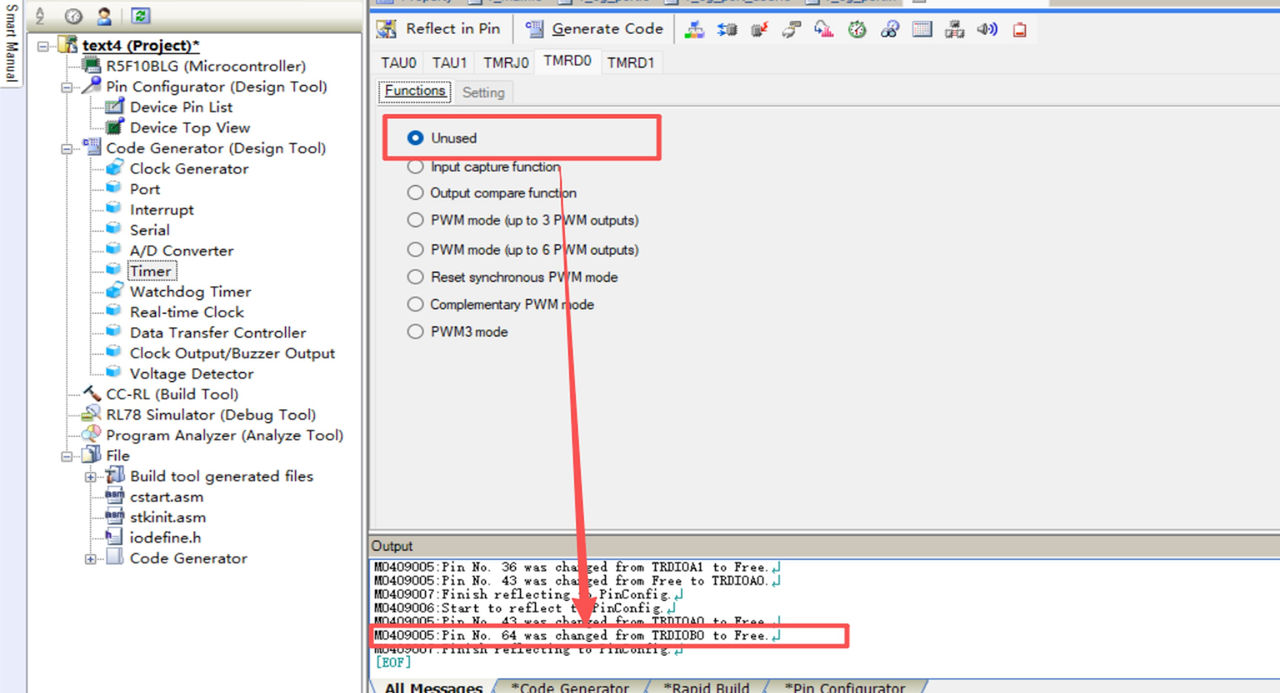

2、勾选 Unused

取消勾选 TRDGRB0 按钮后,点击左上方的【Reflect in Pin】会重新分配引脚,此时下方 command 窗口会提示该引脚从 TRDIOB0 变成了 Free,意味着引脚得到了释放。

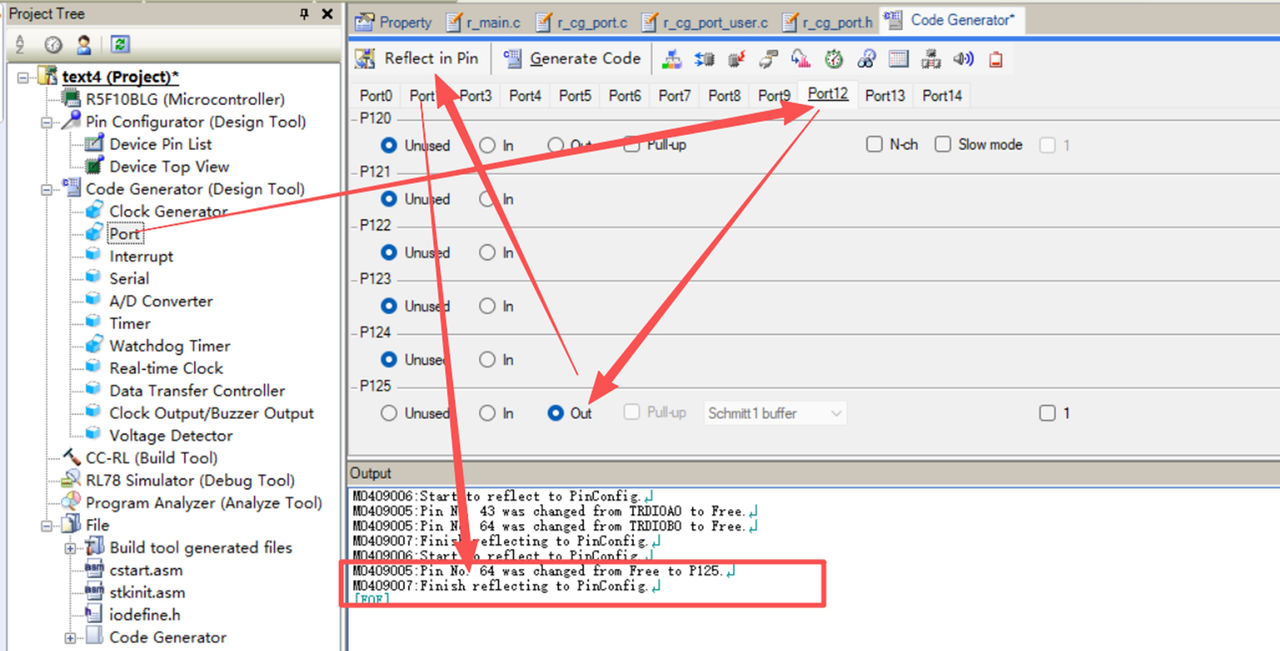

3、重新配置 PORT 并分配引脚

返回【PORT】配置界面,将 PORT 作为输出,再次点击【Reflect in Pin】,command 窗口会提示 pin 脚 64 被作为 P125 功能使用,也就是普通的 I/O PORT,此时配置完成。

其他类似的配置也可以按照这个流程去进行修改和配置。在操作过程中,应密切关注 command 窗口的提示信息,以确保 pin 状态正确变更。

四、总结

本文基于实际项目经验,总结了瑞萨RL78/F13 系列中外设功能与 I/O 冲突的解决方法。通过合理使用 CS+ 的 pin 映射与模块配置功能,可在不更换硬件的前提下灵活调整 PIN 功能,提升系统设计的适应性与开发效率。

欲了解关于更多瑞萨相关方案或技术信息,请与骏龙科技当地的办事处联系或点击下方「联系我们」,提交您的需求,骏龙科技公司愿意为您提供更详细的技术解答。

更多信息: